# Acceleration of Cryptographic Functions using Graphics Hardware

### Owen Harrison

A thesis submitted to the

University of Dublin, Trinity College

for the degree of Doctor of Philosophy

February 2010

### Declaration

I, the undersigned, declare that this work has not previously been submitted to this or any other University, and that unless otherwise stated, it is entirely my own work.

Owen Harrison

Dated: 18<sup>th</sup> February, 2010

# Permission to Lend and/or Copy

I, the undersigned, agree that Trinity College Library may lend or copy this thesis upon request.

Owen Harrison

Dated: 18<sup>th</sup> February, 2010

# Acknowledgements

I would like to thank my family for always being there, unwavering in support. To John Waldron, my supervisor, thank you for giving me the initial opportunity, the freedom I required and well timed advice dotted over the past years. Thanks to my friends for encouraging, sympathising, distracting, entertaining, especially Barry, Claire, Garrett, Niall, Marie and Saar. To Tony, my best man, for many ideas, many comments, much patience, a debt of gratitude I am incapable of repaying. To Rachel, my reader, my open ears, my support, my friend, my wife, thank you, te quiero mucho.

### Abstract

Graphics processing units (GPUs) can act as an attractive alternative to CPUs for general purpose computation in certain scenarios. Traditionally, the GPU has been developed to offload graphics processing from the CPU. In recent years the GPU has continued to become a more flexible and powerful device, responding to the demand of the games industry to execute more and more complex custom graphics algorithms. In the early 2000s a new approach to processing emerged, whereby non-graphics problems that suit a data parallel model could execute on the GPU at competitive or faster rates that the CPU. This performance gap has continued to grow, and as the GPU develops in terms of programming flexibility, the range of application spaces that benefit from GPU assistance widens. Adding to this trend, GPU vendors have started releasing programming frameworks specifically tailored to general purpose computation on GPUs. In light of these developments, there is intense research involving the use of GPUs for acceleration within many problem spaces. We advance the state of the art by presenting the capacity of the GPU to accelerate commonly used cryptographic functions.

We investigate GPU acceleration of symmetric-key and asymmetric-key functions, fundamental components of modern cryptographic systems. We show that AES, a popular example of a symmetric-key function, can be competitive with the CPU on recent GPUs and outperform on contemporary GPUs. We illustrate the issues related to GPU support of symmetric-key modes of operations in various scenarios and present strategies for maintaining performance. We show that RSA, a popular example of an asymmetric-key function, can outperform the CPU when running on the GPU. For both symmetric-key and asymmetric-key approaches presented, not all cryptographic contexts suit the GPU and as such these contexts are highlighted. Also, both approaches are investigated for efficient batching of multiple requests within a single GPU call. Finally, the integration of GPU accelerated cryptography within an operating system abstraction layer and associated costs are presented.

### Related Publications

- O. Harrison and J. Waldron. Efficient Acceleration of Asymmetric Cryptography on Graphics Hardware. *International Conference on Cryptology in Africa, (AfricaCrypt)*, Gammarth, Tunisia, June 21–25, 2009. LNCS, Volume 5580/2009, Pages 350–367.

- O. Harrison and J. Waldron. Public Key Cryptography on Graphics Hardware. Annual International Conference on the Theory and Applications of Cryptographic Techniques, (Eurocrypt), Cologne, Germany, April 26–30, 2009. Appeared in conference booklet, Pages 65–72, and as Poster.

- O. Harrison and J. Waldron. Practical Symmetric Key Cryptography on Modern Graphics Hardware. *USENIX Security Symposium*, San Jose, CA, July 28–August 1, 2008. Pages 195–209.

- O. Harrison and J. Waldron. AES Encryption Implementation and Analysis on Commodity Graphics Processing Units. *Workshop on Cryptographic Hardware and Embedded Systems, (CHES)*, Vienna, Austria, September 10–13, 2007. LNCS, Volume 4727/2007, Pages 209–226.

- O. Harrison and J. Waldron. Optimising Data Movement Rates for Parallel Processing Applications on Graphics Processors. *International Conference on Parallel and Distributed Computing and Networks*, Innsbruck, Austria, February 12–14, 2007. Pages 251–256.

#### Under Review

O. Harrison and J. Waldron. GPU Accelerated Cryptography as an OS Service, September 2009. Currently available as a technical report [45].

# Glossary

AES Advanced Encryption Standard

CBC Cipher Block Chaining MOO

CCM Counter with CBC-Message Authentication Code MOO

CTR Counter MOO

DES Data Encryption StandardDMA Direct Memory Access.

DX9 DirectX 9. Microsoft suite of media APIs. Also used to

identify a generation of compliant graphics hardware.

**DX10** DirectX 10.

ECB Electronic Codebook MOO

ECC Elliptic Curve Cryptography

FLOP Floating Point Operation

GPU Graphics Processing Unit

GPGPU General Purpose Computation on Graphics Processing

Units

**Kb,Mb,Gb** 2<sup>10</sup>,2<sup>20</sup>,2<sup>30</sup> bits **KB,MB,GB** 2<sup>10</sup>,2<sup>20</sup>,2<sup>30</sup> bytes

MOO Symmetric-key Mode of Operation

**NIST** National Institute of Standards and Technology

OCF OpenBSD Cryptographic Framework

**RNS** Residue Number System

**ROP** Raster Operations

RSA Rivest Shamir Adleman asymmetric-key algorithm

SIMD Single Instruction Multiple Data

SIMT Single Instruction Multiple Threads

SM Streaming Multiprocessor SP Streaming Processor

Warp Group of threads issued by the GPU thread scheduler

as a single unit.

**XOR** Exclusive OR

# Contents

| A            | cknov  | wledge                       | ements                                      | iv                     |

|--------------|--------|------------------------------|---------------------------------------------|------------------------|

| $\mathbf{A}$ | bstra  | $\operatorname{\mathbf{ct}}$ |                                             | $\mathbf{v}$           |

| R            | elate  | d Pub                        | lications                                   | vi                     |

| $\mathbf{G}$ | lossaı | ry                           |                                             | vii                    |

| $\mathbf{C}$ | onten  | its                          |                                             | viii                   |

| Li           | st of  | Figur                        | es                                          | xiii                   |

| Li           | st of  | Table                        | ${f s}$                                     | $\mathbf{x}\mathbf{v}$ |

| 1            | Intr   | oduct                        | ion                                         | 1                      |

|              | 1.1    | Thesis                       | s Aim                                       | 3                      |

|              | 1.2    | Motiv                        | ation                                       | 3                      |

|              | 1.3    | Contr                        | ibutions                                    | 4                      |

| 2            | Bac    | kgrou                        | nd and Related Work                         | 7                      |

|              | 2.1    | DX9 (                        | Compliant Graphics Hardware                 | 7                      |

|              |        | 2.1.1                        | Hardware Overview                           | 7                      |

|              |        | 2.1.2                        | Programming Interface                       | 8                      |

|              |        | 2.1.3                        | Textures                                    | 10                     |

|              |        | 2.1.4                        | General Purpose Computation                 | 11                     |

|              |        | 2.1.5                        | Restrictions and Performance Considerations | 12                     |

|              | 2.2    | DX10                         | Compliant Graphics Hardware                 | 15                     |

|              |        | 2.2.1                        | Departure from DX9                          | 15                     |

|              |        | 2.2.2                        | Hardware Overview                           | 16                     |

|              |        |                              | 2.2.2.1 Nvidia DX10 Compliant Hardware      | 17                     |

|              |        | 2.2.3                        | Programming Interface - CUDA                | 19                     |

|              |        | 2.2.4                        | Restrictions and Performance Considerations | 22                     |

|   |     |        | 2.2.4.1 Men    | nory                                          | 22 |

|---|-----|--------|----------------|-----------------------------------------------|----|

|   |     |        | 2.2.4.2 Bran   | nching                                        | 25 |

|   |     |        | 2.2.4.3 Three  | ead Co-operation                              | 26 |

|   |     |        | 2.2.4.4 Occi   | ipancy                                        | 26 |

|   |     |        | 2.2.4.5 Inst   | ruction Throughput                            | 29 |

|   |     |        | 2.2.4.6 Data   | a Transfer                                    | 29 |

|   |     |        | 2.2.4.7 Exec   | cution Model                                  | 30 |

|   |     |        | 2.2.4.8 Tool   | Chain                                         | 31 |

|   |     | 2.2.5  | Shader Model   | $3.0$ versus Shader Model $4.0 \ldots \ldots$ | 31 |

|   | 2.3 | Symm   | etric-Key Cryp | otography                                     | 32 |

|   |     | 2.3.1  | AES            |                                               | 33 |

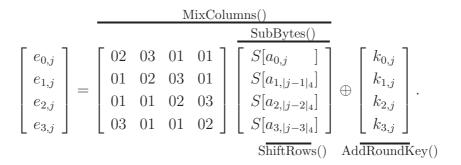

|   |     |        | 2.3.1.1 Sing   | le Cipher Round                               | 33 |

|   |     |        | 2.3.1.2  Full  | Cipher                                        | 36 |

|   |     |        | 2.3.1.3 Imp    | lementation                                   | 36 |

|   |     | 2.3.2  | Block Cipher   | Modes of Operations                           | 38 |

|   |     |        | 2.3.2.1 Para   | ıllel Modes                                   | 38 |

|   |     |        | 2.3.2.2 Seria  | al Modes                                      | 39 |

|   | 2.4 | Asymı  | netric-Key Cry | ptography                                     | 40 |

|   |     | 2.4.1  | RSA            |                                               | 41 |

|   |     | 2.4.2  | Modular Arit   | hmetic Fundamentals                           | 43 |

|   |     |        | 2.4.2.1 Basi   | cs                                            | 43 |

|   |     |        | 2.4.2.2 Chir   | nese Remainder Theorem                        | 44 |

|   |     |        | 2.4.2.3 Integ  | ger Representation                            | 44 |

|   |     |        | 2.4.2.4 Mon    | tgomery Reduction                             | 46 |

|   |     |        | 2.4.2.5 Exp    | onentiation                                   | 47 |

|   | 2.5 | Relate | d Work         |                                               | 49 |

|   |     | 2.5.1  | Cryptography   | and Graphics Hardware                         | 49 |

|   |     |        | 2.5.1.1 Sym    | metric-Key Cryptography                       | 49 |

|   |     |        | 2.5.1.2 Asyr   | mmetric-Key Cryptography                      | 54 |

|   |     |        | 2.5.1.3 Oth    | er                                            | 55 |

| 3 | GPI | ∐ Data | Transfer       |                                               | 57 |

|   | 3.1 |        |                | peline                                        | 58 |

|   | 3.2 |        |                |                                               | 60 |

|   | 3.3 |        |                |                                               | 61 |

|   |     | 3.3.1  |                |                                               | 61 |

|   |     | 3.3.2  |                |                                               | 61 |

|   |     | 3.3.3  |                |                                               | 63 |

|   |     | 3.3.4  | _              |                                               | 63 |

|   |     |        |                |                                               |    |

|   | 3.4 | Readback Tool                               | 66            |

|---|-----|---------------------------------------------|---------------|

|   |     | 3.4.1 Overview                              | 36            |

|   |     | 3.4.2 Transfer Rate Mode                    | 66            |

|   |     | 3.4.3 Asynchronous Behaviour Mode           | 67            |

|   |     | 3.4.4 Usage Notes                           | <sub>59</sub> |

|   |     | 3.4.5 Observations                          | 70            |

|   |     | 3.4.5.1 Transfer Rate Observations          | 70            |

|   |     | 3.4.5.2 Asynchronous Behaviour Observations | 70            |

|   | 3.5 | DX10 Data Transfer                          | 72            |

|   | 3.6 | Conclusions                                 | 72            |

| 4 | Syn | nmetric Cryptography on DX9 Hardware 7      | 73            |

|   | 4.1 | The GPU and AES                             | 74            |

|   | 4.2 |                                             | 77            |

|   |     |                                             | 77            |

|   |     | 4.2.2 4-bit XOR                             | 77            |

|   |     | 4.2.3 ROP XOR                               | 79            |

|   |     |                                             | 79            |

|   | 4.3 |                                             | 30            |

|   |     | 4.3.1 AES Lookup Tables                     | 30            |

|   |     |                                             | 31            |

|   |     | 4.3.3 AES Implementations                   | 32            |

|   |     | 4.3.4 Results                               | 36            |

|   | 4.4 | GPU as an AES Co-Processor                  | 90            |

|   |     | 4.4.1 Results                               | 91            |

|   | 4.5 |                                             | 91            |

| 5 | Syn | nmetric Cryptography on DX10 Hardware       | 93            |

|   | 5.1 | Block Based AES Implementation              | 94            |

|   |     | 5.1.1 Mapping AES to CUDA                   | 94            |

|   |     |                                             | 96            |

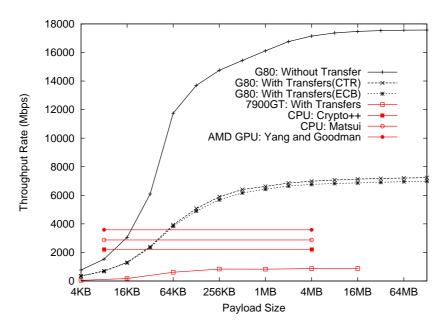

|   |     | 5.1.3 Results                               | 00            |

|   | 5.2 | Payload Data Model                          |               |

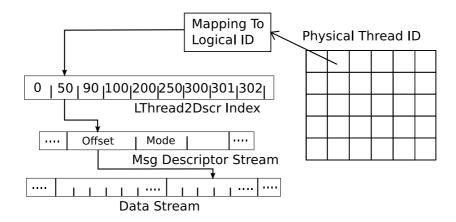

|   |     | 5.2.1 The Data Model                        | )4            |

|   |     | 5.2.2 General Use Implications              |               |

|   | 5.3 | Applied Data Model                          |               |

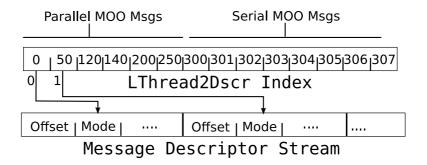

|   |     | 5.3.1 Descriptor Serialisation              |               |

|   |     | 5.3.2 Thread to Message Mapping             |               |

|   |     | 5.3.3 Padding                               |               |

|   |     | 5.3.4  | Payload Combining                                         |

|---|-----|--------|-----------------------------------------------------------|

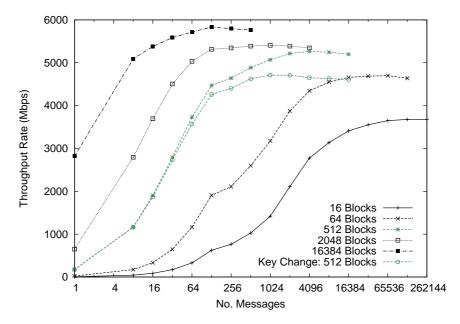

|   | 5.4 | Modes  | s Of Operation                                            |

|   |     | 5.4.1  | Parallel MOOs                                             |

|   |     | 5.4.2  | Serial MOOs                                               |

|   |     | 5.4.3  | Mixed MOOs and Message Sizes                              |

|   | 5.5 | Conclu | asions                                                    |

| 6 | Asy | mmeti  | ric Cryptography on DX10 Hardware 121                     |

|   | 6.1 | Imple  | mentation Commonalities                                   |

|   | 6.2 | Radix  | Based Modular Exponentiation                              |

|   |     | 6.2.1  | Serial Approach                                           |

|   |     |        | 6.2.1.1 Memory Usage                                      |

|   |     |        | 6.2.1.2 Results                                           |

|   |     | 6.2.2  | Parallel Approach                                         |

|   |     | 6.2.3  | Radix Results                                             |

|   | 6.3 | RNS I  | Based Modular Exponentiation                              |

|   |     | 6.3.1  | Montgomery in RNS                                         |

|   |     | 6.3.2  | Exponentiation using Kawamura on the GPU 135              |

|   |     | 6.3.3  | Single Precision Modular Multiplication on the GPU $$ 139 |

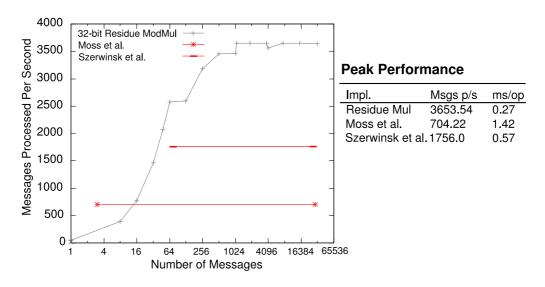

|   |     |        | 6.3.3.1 Results                                           |

|   |     | 6.3.4  | RNS Results                                               |

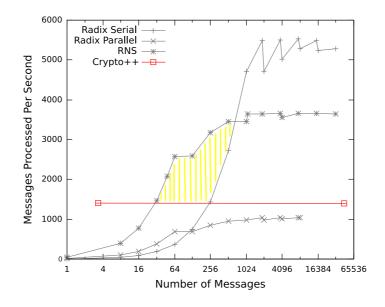

|   | 6.4 | Radix  | vs RNS on the GPU                                         |

|   | 6.5 | Conclu | asions                                                    |

| 7 | GP  | U Acce | elerated Cryptography as an OS Service 147                |

|   | 7.1 | OCF I  | Background                                                |

|   | 7.2 | _      | ation of GPU and OCF                                      |

|   |     | 7.2.1  | Overview                                                  |

|   |     | 7.2.2  | Memory Management                                         |

|   |     |        | 7.2.2.1 Memory Map Creation                               |

|   |     |        | 7.2.2.2 Memory Map Removal                                |

|   |     |        | 7.2.2.3 Memory Map Translation                            |

|   |     | 7.2.3  | GPU Driver and Daemon                                     |

|   |     | 7.2.4  | Security                                                  |

|   | 7.3 | Concu  | rrent Request Processing                                  |

|   |     | 7.3.1  | Symmetric Request Batching                                |

|   |     | 7.3.2  | Asymmetric Request Batching                               |

|   |     | 7.3.3  | Request Pipelining                                        |

|   | 7.4 | Perfor | mance                                                     |

|              |      | 7.4.1 Symmetric-Key Performance       | 165 |

|--------------|------|---------------------------------------|-----|

|              |      | 7.4.2 Asymmetric-Key Performance      | 168 |

|              | 7.5  | Conclusions                           | 169 |

| 8            | Rev  | riew and Outlook                      | 171 |

|              | 8.1  | General Lessons                       | 175 |

|              | 8.2  | Future Work                           | 177 |

| Aı           | ppen | dices                                 | 190 |

| $\mathbf{A}$ | OC   | F Extensions                          | 190 |

|              | A.1  | New Memory Management Interface       | 190 |

|              |      | A.1.1 Crypto Layer Interface          | 190 |

|              |      | A.1.2 Cryptodev Layer ioctl Interface | 190 |

|              | A.2  | Gpucrypt ioctl Interface              | 190 |

| В            | Har  | ${ m cdware}$                         | 192 |

|              | B.1  | Processor Details                     | 192 |

|              | B.2  | Memory Bandwidth                      | 192 |

|              | B.3  | GeForce 8800GTX Memory                | 192 |

| $\mathbf{C}$ | Оре  | erating System Terms and Functions    | 194 |

| D            | Syst | tem Specifications                    | 197 |

# List of Figures

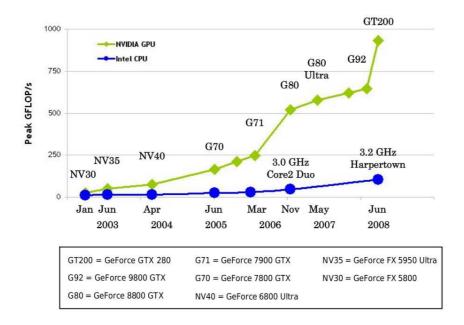

| 1.1  | Floating point performance for Nvidia GPUs and Intel CPUs [93].                                                   | 2  |

|------|-------------------------------------------------------------------------------------------------------------------|----|

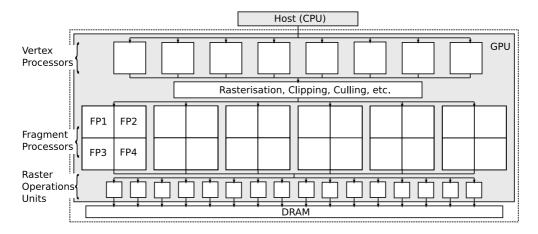

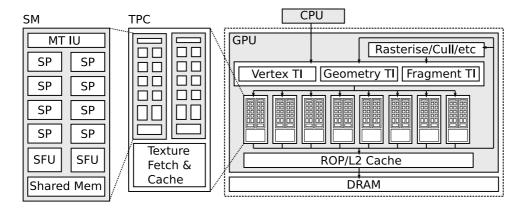

| 2.1  | Simplified block diagram of the GeForce 7900GTX, a DX9 compliant GPU                                              | 8  |

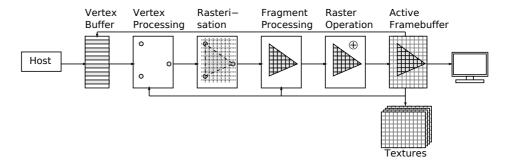

| 2.2  | The different stages of the DX9 graphics pipeline                                                                 | 9  |

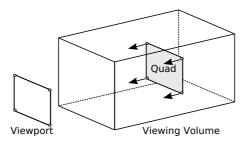

| 2.3  | Orthogonal projection configured to protect the co-ordinates of the input vertices                                | 12 |

| 2.4  | Simplified block diagram of the GeForce 8800GTX, the first DX10 compliant GPU                                     | 16 |

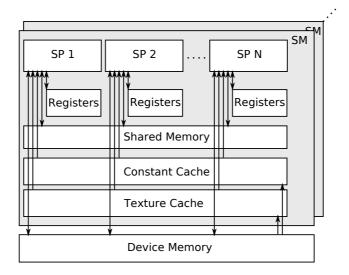

| 2.5  | Block diagram of the physical memory available to the SPs on a G8X GPU                                            | 18 |

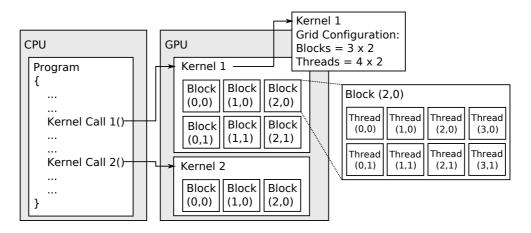

| 2.6  | Example of the CUDA execution model                                                                               | 21 |

| 2.7  | State for AES-128: input and output for round transformations                                                     | 33 |

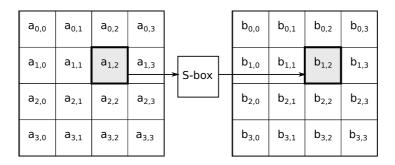

| 2.8  | AES-128 SubBytes byte substitution using an S-box lookup                                                          | 34 |

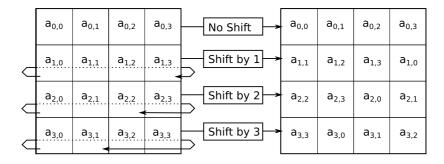

| 2.9  | AES-128 ShiftRows round transformation stage                                                                      | 34 |

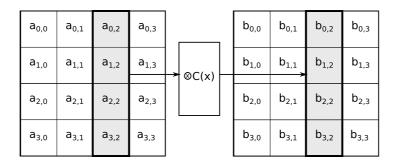

| 2.10 | AES-128 MixColumns round transformation stage                                                                     | 35 |

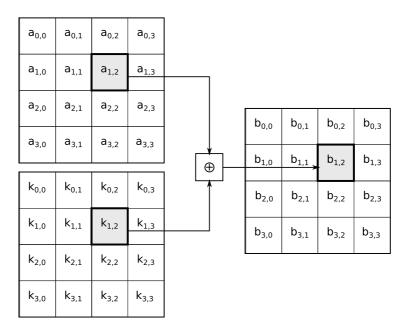

| 2.11 | AES-128 AddRoundKey round transformation stage                                                                    | 35 |

| 2.12 | Electronic Code Book Mode of Operation: encryption and decryp-                                                    |    |

|      | tion                                                                                                              | 38 |

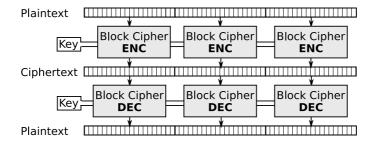

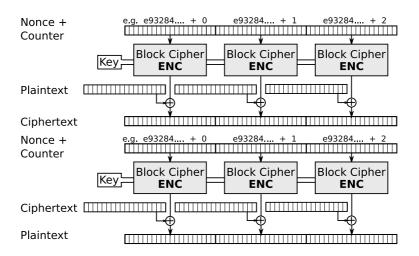

|      | Counter Mode of Operation: encryption and decryption Cipher Block Chaining Mode of Operation: encryption and de-  | 39 |

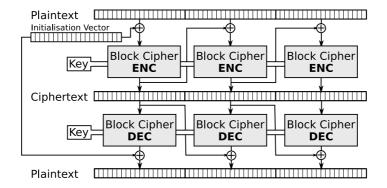

|      | cryption                                                                                                          | 40 |

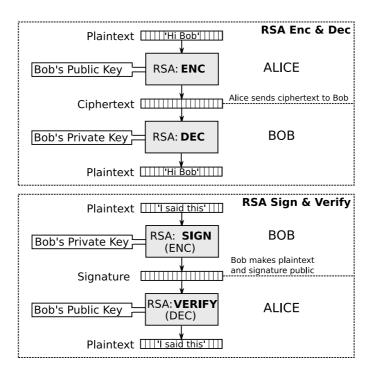

| 2.15 | Example of Public and Private Key use in RSA                                                                      | 41 |

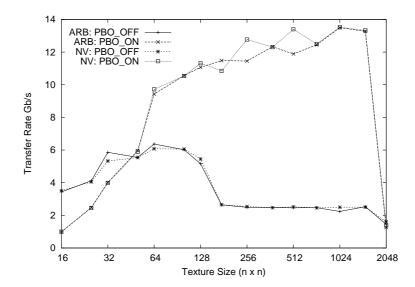

| 3.1  | Download rates for varying texture sizes, with 4 component FP32 texels, across different scenarios using a 6600GT | 65 |

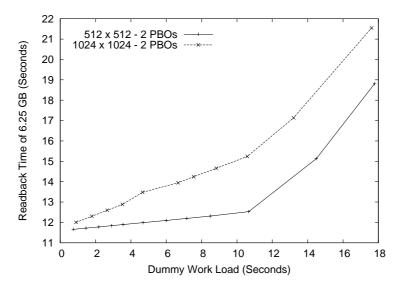

| 3.2  | PCIe asynchronous behaviour comparison of $512 \times 512$ versus $1024 \times 1024$ buffers                      | 71 |

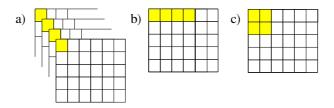

| 4.1  | Illustrations of the different gather techniques employed for message input data across the AES approaches        | 82 |

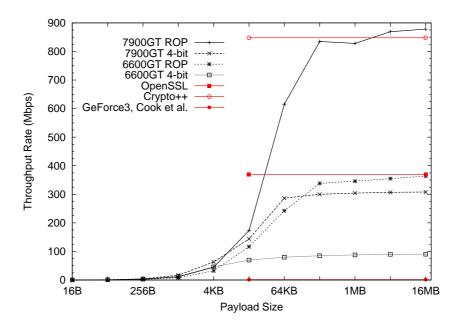

| 4.2  | Effects of payload size variation on AES encryption throughput 87                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------|

| 5.1  | G80 AES implementations with and without data transfers across varying payload sizes                                             |

| 5.2  | Serialised streams used by each thread for data and key retrieval. 109                                                           |

| 5.3  | · · · · · · · · · · · · · · · · · · ·                                                                                            |

| 5.4  | Mapping physical thread IDs to descriptor IDs to message data 110 Throughput rates for parallel MOO messages across varying mes- |

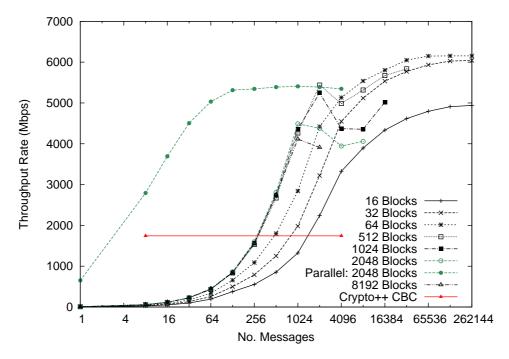

| 0.4  | sage numbers and sizes                                                                                                           |

| 5.5  | Throughput rates for serial MOO messages across varying message                                                                  |

| 0.0  | numbers and sizes                                                                                                                |

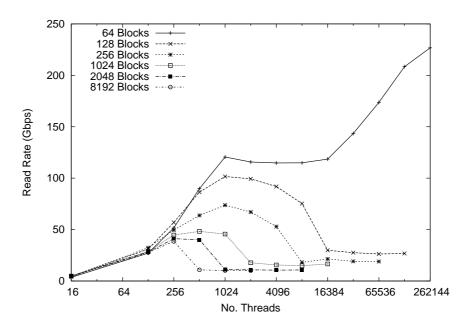

| 5.6  | Global memory read performance with varying stride patterns 117                                                                  |

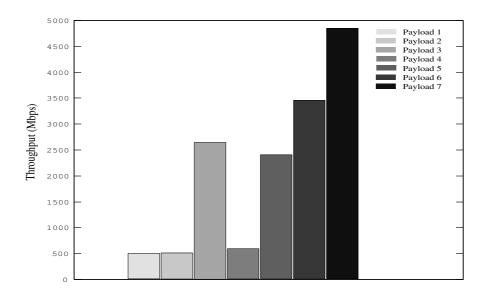

| 5.7  | Throughput rates for different payload packing configurations 118                                                                |

| 0.1  | Throughput rates for different payload packing configurations 110                                                                |

| 6.1  | Serial Thread Model                                                                                                              |

| 6.2  | $N{\times}N$ limb multiplication in parallel on a CUDA device 130                                                                |

| 6.3  | GPU Radix based Montgomery Exponentiation: 1024-bit RSA                                                                          |

|      | Decryption                                                                                                                       |

| 6.4  | GPU RNS based Montgomery Exponentiation: 1024-bit RSA De-                                                                        |

|      | cryption                                                                                                                         |

| 6.5  | RNS vs Radix: 1024-bit RSA Decryption                                                                                            |

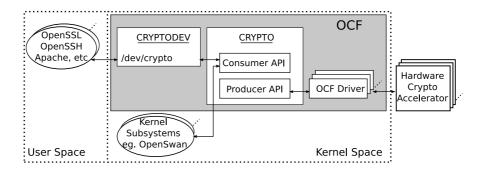

| 7.1  | Original OCF Architecture                                                                                                        |

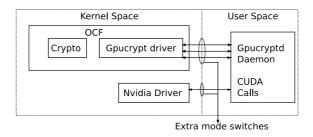

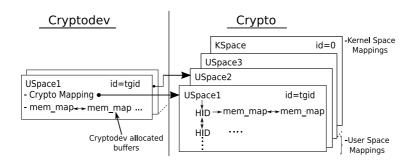

| 7.2  | OCF and GPU: High Level View - Different Address Space Problem.150                                                               |

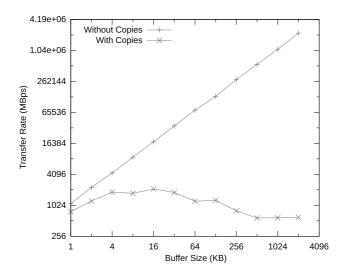

| 7.3  | Illustration of the Cryptodev Layer Memory Management Overhead. 151                                                              |

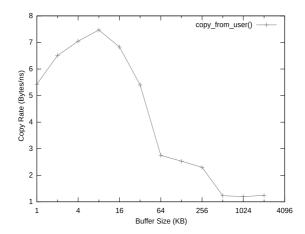

| 7.4  | Performance of the copy_from_user() Function                                                                                     |

| 7.5  | Crypto and Cryptodev Layers: Memory Mapping Internal Structure. 153                                                              |

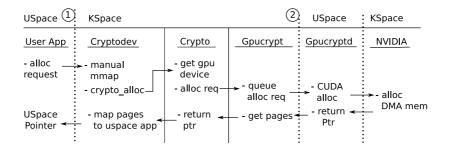

| 7.6  | New OCF Memory Allocation: Cryptodev to GPU 154                                                                                  |

| 7.7  | Crypto and Cryptodev Layers: Memory Mapping Translation Pro-                                                                     |

|      | cess                                                                                                                             |

| 7.8  | GPU Driver Gpucrypt and GPU Daemon Gpucrypt<br>d 157                                                                             |

| 7.9  | Mechanism for Processing Multiple Distinct Asymmetric-Key Re-                                                                    |

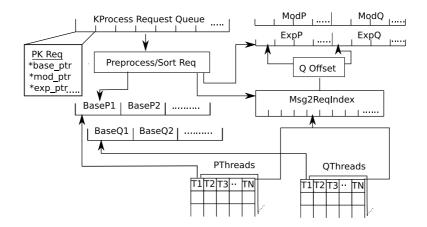

|      | quests                                                                                                                           |

| 7.10 | Comparison of Pre-processing techniques for RSA-1024 Request                                                                     |

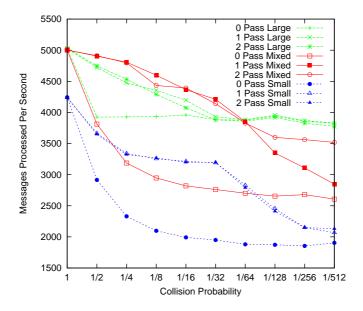

|      | Batching                                                                                                                         |

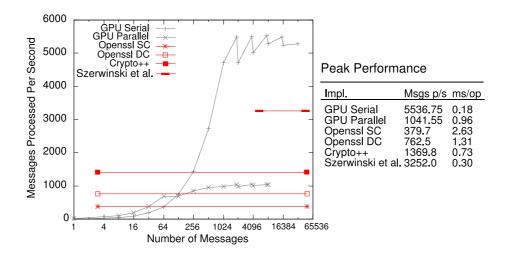

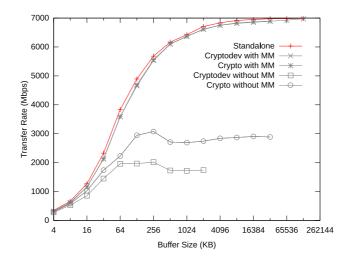

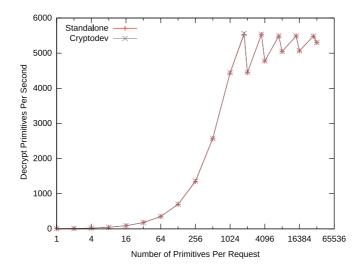

| 7.11 | Performance of GPU accelerated AES using the OCF 165 $$                                                                          |

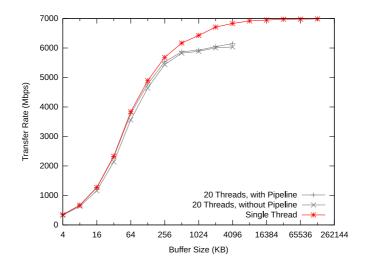

| 7.12 | Multithreaded performance of GPU accelerated AES using the OCF. $167$                                                            |

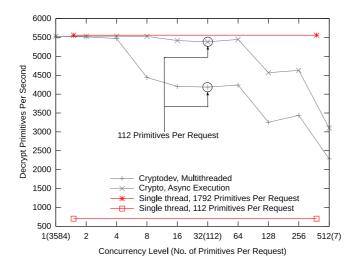

| 7.13 | Performance of GPU accelerated RSA-1024 using the OCF 167 $$                                                                     |

| 7.14 | Concurrency and GPU accelerated RSA-1024 using the OCF 168                                                                       |

# List of Tables

| 2.1 | Comparison of select features required by DX9 Shader Model 3.0 and DX10 Shader Model 4.0 | 31       |

|-----|------------------------------------------------------------------------------------------|----------|

| 3.1 | Example output of the readback tool in asynchronous behaviour mode using a 6600GT        | 68       |

| 4.1 | Peak data transfer rates using $1024 \times 1024$ , 4 component, byte                    |          |

| 4.2 | downloadBench and $readbackBench$ parameters used in pipeline                            | 74       |

| 4.3 | configuration of AES implementations                                                     | 75       |

| 4.4 | Gb/s of XOR output                                                                       | 80       |

|     | using simulated XOR in-fragment processor operation                                      | 84       |

| 4.5 | GeForce 6600GT results for the various AES approaches quoted in Mb/s                     | 86       |

| 4.6 | GeForce 7900GT results for the various AES approaches quoted                             |          |

| 4.7 | ,                                                                                        | 86<br>90 |

| 4.8 | -                                                                                        | 91       |

| 5.1 |                                                                                          | 95       |

| 5.2 | On-chip Memory Reads: Average execution times for 5 billion 32-bit integer reads         | 98       |

| 5.3 | Modification of values used for AES lookup table indexes to avoid                        |          |

| 5.4 | AES CTR peak throughput rate on the G80, including data trans-                           | 99       |

| 5.5 |                                                                                          | .00      |

| 6.1 | Kawamura et al. [53]: Montgomery multiplication in an RNS 1                              | 34       |

| 6.2 | CUDA thread allocation scheme for RNS based modular exponen-           |

|-----|------------------------------------------------------------------------|

| 0.2 | -                                                                      |

|     | tiation                                                                |

| 6.3 | Granlund and Montgomery's division by invariants optimised for         |

|     | GPU and RNS                                                            |

| 6.4 | GPU Modular Multiplication throughput using a variety of tech-         |

|     | niques                                                                 |

| B.1 | List of CPUs used for comparisons                                      |

| B.2 | Bandwidth rates between relevant GPUs and on-card device mem-          |

|     | ory                                                                    |

| В.3 | Bandwidth rates of relevant system bus types                           |

| B.4 | Physical memory types and sizes for the GeForce $8800\mathrm{GTX}$ 193 |

| D.1 | System 1                                                               |

| D.2 | System 2                                                               |

| D.3 | System 3                                                               |

# Chapter 1

### Introduction

Graphics processing units (GPU) have exhibited a large increase in floating point performance compared with traditional CPUs since the early 2000s. The traditional CPU has levelled off in terms of clock frequency as power and heat concerns have become dominant restrictions. A 2008 GPU released by Nvidia reports a peak throughput of almost 1 TeraFlop. In contrast, a similar era quad core Intel x86 CPU reports a peak throughput in the order of 100 GigaFlops. The continuing divergence of floating point performance is made clear by Figure 1.1. The performance advantage of the GPU over the CPU comes at a price of decreased applicability to general purpose computing. The CPU is optimised for general purpose serial processes. Large on-chip caches and complex control logic are used to hide system memory access latencies. This leads to a large amount of the x86 transistor budget being consumed by caches and control logic. The GPU in comparison contains a reduced amount of on-chip caches and control logic and in return there is an increased percentage of transistor logic spent on execution units. For example, the latest Nvidia GPU contains 240 simple processing cores. This division of transistor budget narrows the GPU's suitability to tasks that are data parallel and exhibit a high compute intensity.

A data parallel task is one where multiple threads can be instantiated, all executing the same programme, across many data elements in parallel. An example of such a task is graphics rendering, where there exists a number of input data elements and a single shading program that executes in parallel across the input elements to generate pixels. A task exhibiting a high compute intensity, or arithmetic intensity, is one with a high ratio of arithmetic to memory access instructions. Memory latency on the GPU is expected to be hidden by a combination of arithmetic instructions and a high number of parallel threads, rather than large caches and control logic. Tasks that fit the data parallel and compute intensity criteria can exhibit higher performance on a GPU compared to a CPU.

Figure 1.1: Floating point performance for Nvidia GPUs and Intel CPUs [93].

An important trend, which broadens the GPUs suitability to general computation, is the increasing ability to program the processors. Early GPUs were fixed function devices, supporting a graphics pipeline via parametrisation only. Subsequent generations introduced programmable units within the GPU, primarily to allow game programmers to execute custom code for pixel shading. Each generation further increased the flexibility of these programmable units. Examples include increases in supported program length, increases in register counts, addition of branch instructions and improved memory access. Early recognition of the possibility of using the GPU as a general purpose data parallel, or stream, processor came from Buck et al. [12] and Venkatasubramanian [125] in 2003.

An early important milestone for general purpose computation on GPUs (GPGPU) was the release of Shader Model 3.0 [107] compliant processors. Shader Model 3.0 is part of Microsoft's DirectX 9 [71] suite of programming interfaces and details the feature set of the programmable units within a GPU. These GPUs, released by both the major GPU vendors, Nvidia and AMD (formerly ATI), improved the flexibility of the programming units to the extent where they could realistically compete with the traditional CPU with regard to performance on suitable compute intensive parallel problems. Early examples of GPGPU include work in diverse fields such as databases [34], computer vision [30] and data mining [36]. One of the most popular GPGPU projects, Folding@home [28], used a DirectX 9 compliant GPU to achieve a ~2.5 times increase over a comparable CPU. The next major milestone for GPGPU was the introduction of Shader

Model 4.0 [73] complaint GPUs in 2006. This standard further pushed the capabilities of the programmable units within the GPU to resemble fully featured CPUs. GPU vendors also recognised the market for general computation acceleration by releasing non graphical APIs to program their devices for the first time. From this point on, the interest in GPGPU has intensified, spreading to a large number of application contexts [37].

The increase in pervasiveness of confidential online transactions, digital rights management solutions and the secure digitisation of all forms of governmental, corporate and personal data, drives the demand for efficient security systems. The high speed implementation of cryptographic algorithms used to form such systems continues to be an active area of research. Such implementations are not only limited to the CPU, but are also based on an array of diverse hardware devices such as FPGAs, ASICs, PCI co-processor cards, RFID, smart cards and USB devices [26]. Two common types of constituent algorithms in security systems are symmetric-key and asymmetric-key. Symmetric-key algorithms are generally used for confidential communication between parties in the case where a shared secret between the parties exists. Asymmetric-key algorithms are generally used for confidential communication between parties where no shared secret exists. These algorithm types are combined in various ways to produce secure systems providing authenticity, integrity and confidentiality. Symmetric-key and especially asymmetric-key algorithms can exhibit a high compute intensity, and in certain circumstances, a suitability to highly parallel compute devices.

#### 1.1 Thesis Aim

The aim of this thesis is to investigate to what extent the GPU can act as an efficient cryptographic processing platform for symmetric-key and asymmetric-key algorithms. The focal algorithms for this investigation are two of the most popular cryptographic functions, AES [79] (symmetric-key) and RSA [111] (asymmetric-key).

### 1.2 Motivation

The GPU is now ubiquitous, but for the most part it is grossly underutilised. Unless playing high-end games, in the order of a TeraFlop of processing power is largely going unused. There exists the potential to use this available power in the capacity of a co-processor for non-graphical processing. In particular, it could possibly fulfil the role of existing PCI-based cryptographic accelerator

cards. Standard end-user machines could potentially offload their cryptographic requirements to the GPU, freeing up the CPU for other tasks. Applications within a server environment requiring bulk cryptographic processing, such as secure backup/restore or high bandwidth media streaming, could similarly benefit. Also, it is important that potential sources of high performance cryptographic processing are benchmarked. This provides the metrics against which the security assumptions of the various cryptographic primitives are scrutinised. A further motivation for employing the GPU to perform cryptographic tasks is the possibility of creating a reduced trusted computing base that is designed to hide data from the CPU. This could be used for example in the transfer of encrypted video feeds, which are decrypted directly on the GPU. The potential for such a system has been discussed by Cook et al. [14].

A background motivation for this work is related to the traditional CPU design bottlenecking on clock frequency. The main technique employed to tackle this problem is to increase the number of on-chip processing cores, thereby increasing the total amount of available clock cycles. Intel are currently developing "many core" architectures within the Terascale and Larrabee projects. Terascale has demonstrated an 80-core processor as a research prototype. Larrabee is yet to be released as a commercial product, though published architecture designs [117] show it to be a highly parallel processor aimed at graphics tasks and general purpose compute intensive tasks. AMD are also developing a hybrid processor within their Fusion project, combining on a single die a traditional CPU design with a many core GPU-like design for parallel work [3]. It seems likely that future general purpose computation will involve some form of highly parallel compute device. The GPU, currently with 240 on-chip processing cores, can be seen as an early example of such a device. Future parallel devices are likely to follow similar design paths, with many simple arithmetic logic units (ALU) tied to small caches. As such, by mapping cryptography to GPUs, we also hope to expose the issues that this type of processing will encounter in such future highly parallel architectures.

#### 1.3 Contributions

Interest in cryptography on graphics hardware has increased in recent years, especially with the introduction of DirectX 10 compliant GPUs. In Chapter 2 we give the first comprehensive survey of published work related to cryptographic acceleration on graphics hardware. The work in this thesis covers acceleration of cryptographic functions on DirectX 9 and DirectX 10 compliant GPUs. Prior

to DirectX 10, the only method of programming graphics processors was via a graphics API such as via DirectX or OpenGL [97]. Because of its operating system agnostic status, we used OpenGL to program the DirectX 9 compliant devices. During the implementation of AES on such hardware, it became apparent that one of the primary performance bottlenecks was efficient movement of data to and from the graphics card over the system bus. Furthermore, achieving optimal transfer rates for a task using a graphics API is complex, involving the careful selection from a vast array of configuration combinations. No tools existed to help with the selection of such configuration states as little demand exists for bi-directional large data transfers from traditional graphics applications. Chapter 3 is based on work from "Optimising Data Movement Rates For Parallel Processing Applications On Graphics Processors" [41]. This introduces new tools that are used to investigate data movement rates, performance cliff avoidance, and the minimisation of data transfer bottlenecks in our AES implementations.

Chapter 4 is based on work presented in "AES Encryption Implementation and Analysis on Commodity Graphics Processing Units" [40]. It describes the first DirectX 9 compliant GPU implementation of a symmetric-key function that gives competitive performance compared to the traditional CPU. AES is implemented using various approaches in an effort to work around the lack of integer support on the GPUs involved. We also investigate an issue raised by Cook et al. [15], whereby the OS reports 100% usage when executing their OpenGL based AES implementation. We look into this more deeply and show the extent to which the CPU can offload cryptographic operations to the GPU and free cycles for other work.

Chapter 5 presents work from "Practical Symmetric Key Cryptography on Modern Graphics Hardware" [43]. Here, a DirectX 10 compliant GPU is used to implement the fastest reported AES implementation on a GPU. The various issues involved with a high-speed implementation on a DirectX 10 compliant GPU are discussed. The results are compared to CPU implementations and are shown to be favourable. Also presented is a new model for mapping symmetric-key client requests to the GPU in a generic manner. We also study the GPU's ability to process symmetric-key requests within the context of various modes of operation. A mode of operation acts as a wrapping protocol specifying how to use an underlying symmetric-key cipher securely.

Work that first appeared in booklet format in Eurocrypt 2009 as "Public Key Cryptography on Graphics Hardware" [46] and later in Africacrypt 2009 as "Efficient Acceleration of Asymmetric Cryptography on Graphics Hardware" [44] is presented in Chapter 6. This describes one of the first DirectX 10 GPU im-

plementations of efficient big integer modular exponentiation suitable for use in many asymmetric-key cryptographic systems. We show how careful use of the GPU memory system can increase performance and greatly reduce latency over superficially similar GPU implementations. We analyse different number representation systems with an aim to finding a balance between peak performance and minimum latency. In the context of modular exponentiation using residue number systems we introduce new and optimised algorithms for various parts of the implementation. Our GPU exponentiation approaches are employed in an RSA context and are shown to give superior performance compared with CPU based implementations.

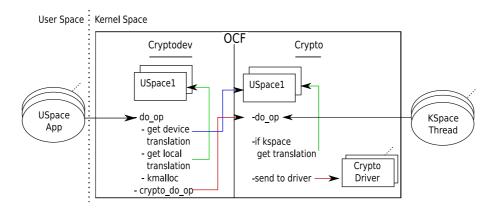

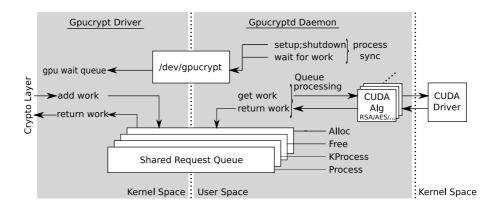

Chapter 7 describes the integration of the GPU as an Operating System service for use by both userspace and kernelspace consumers. An existing virtualisation services layer, the OpenBSD Cryptographic Framework (OCF) [55], which abstracts clients from hardware accelerated cryptographic processors, is used as the basis of this work. The novel contributions are, the effective integration of the GPU within the OCF model; the observation that the GPU interface is userspace only and the newly developed mechanisms to allow it to be used as part of a kernel service; the introduction of a new memory management system within the OCF to allow efficient handling of memory transfers between multiple address spaces; and an implementation of a general purpose multi-request batching scheme for asymmetric key requests with regard to the GPU. This work is under peer review and is currently made available as the technical report, "GPU Accelerated Cryptography as an OS Service" [45].

# Chapter 2

# Background and Related Work

The research presented in this thesis involves the use of two different types of GPU architecture. The first type of architecture concerns GPUs that are DirectX 9 compliant, we label these GPUs as DX9. The second type concerns the use of newer GPUs that are DirectX 10 [70] compliant, labelled DX10. Firstly, this chapter covers an introduction to both architectures, highlighting design features relevant to the implementations presented in subsequent chapters. Secondly, we present the required background to the cryptographic functions explored and related mathematics. Finally, related work in the area of GPUs and cryptography is covered. The GPU information below is generally Nvidia-centric due to the implementations presented in subsequent chapters being based on Nvidia hardware. Nvidia were the first to release DX10 compliant hardware and as such were the vendor of choice for most early DX10 based GPGPU research.

### 2.1 DX9 Compliant Graphics Hardware

#### 2.1.1 Hardware Overview

With respect to Nvidia hardware, DX9 compliant GPUs include all instances of the NV4X [85] and G7X [88] architecture families. These processor families are largely outdated at the time of writing by newer DX10 compliant processors, however many are still in use. For example, the GPU used within Sony's PlayStation 3 is a DX9 GPU based on the Nvidia GeForce 7800GTX, part of the G7X family. GPUs are designed to suit the concept of a graphics pipeline, which traditionally receives as input a description of a 3D model and outputs a 2D rendering for display on screen. Figure 2.1 shows a heavily simplified hardware view of a DX9 compliant GPU, the GeForce 7900GTX, a high-end GPU from the Nvidia G7X family. The figure depicts the main programmable units within

Figure 2.1: Simplified block diagram of the GeForce 7900GTX, a DX9 compliant GPU.

the GPU, the vertex and fragment processors, which support the execution of custom code. The corresponding components within graphics processors prior to DX9 were largely fixed function and were controlled by parameterisation. This allowed little scope for the GPU to be used for anything other than its primary graphics function.

The DX9 vertex and fragment processors contain the majority of the processing power found within a GPU. The distribution of this processing power is not shared evenly between the two types of processing units. Typical graphics applications place more demand for processing on the fragment processors and thus most of the processing power lies within these units. For example, the GeForce 7900GTX is equipped with 24 fragment processors, each of which contains (amongst other components) two 32-bit floating point (FP32) 4-vector arithmetic logic units (ALU). Thus, the fragment processors provide 48 FP32 4-vector ALUs. In comparison, the vertex processors provide 8 equivalent FP32 4-vector ALUs. Figure 2.1 also depicts the raster operations units (ROP). These units are responsible for committing fragment processor output to device DRAM memory.

#### 2.1.2 Programming Interface

Programming DX9 compliant processors requires the use of a graphics APIs such as Direct3D [39], part of the DirectX family of APIs, or OpenGL. These graphics APIs use a programming pipeline, which supports the configuration of the data processing and I/O stages within the GPU. This pipeline, shown in Figure 2.2, is divided into vertex processing, rasterisation, fragment processing and raster

Figure 2.2: The different stages of the DX9 graphics pipeline.

operation processing stages. One can see the parallels between the hardware components discussed above and the programming pipeline. The operation and data in each pipeline stage can be summarised as follows:

- A list of vertices, which exist within a 3 dimensional space, is provide to the graphics driver. These vertices act as descriptors for primitives such as points, triangles or quadrilaterals.

- The vertex processing stage of the pipeline transforms the vertex co-ordinates into screen space co-ordinates.

- The rasterisation stage is responsible for accepting the screen space coordinates, which represent primitives, and generating a pixelised view. This pixelised view comes in the form of arrays of fragments. A fragment denotes a potential pixel, which may or may not be rendered to a final output buffer.

- The fragment processing stage accepts fragments as input and can manipulate attributes of each fragment, such as colour.

- These fragments are outputted to the final stage, raster operation, which is ultimately responsible for writing the final pixel colour values to memory for display or recycling back into the pipeline.

As mentioned, the DX9 vertex and fragment processors are programmable. The vertex processing stage runs custom code, called a *vertex shader*, for each input vertex. The code can specify a series of input and output vertex attributes, such as position, normal, texture co-ordinates and colour. The rasteriser interpolates the output attributes of each vertex within a primitive, generating fragments with a set of interpolated attributes. The fragment processing stage runs custom code, called a *fragment shader*, for each fragment handed off to it by the rasteriser. It is responsible for combining the fragment attributes to generate

a limited number of colour values for handoff to the raster operations units. Various high level shading languages exist for writing shaders, including Microsoft's DirectX High Level Shading Language HLSL [72], OpenGL's shading language GLSL [113] and Nvidia's Cg [66]. These languages provide a C-like environment to program the GPU's vertex or fragment processors. They also provide explicit support for GPU related features such as textures, vector data types, colours and co-ordinates. Shader Model 3.0, part of the DirectX 9.0c specification, details the minimum feature set that both the vertex and fragment processors support. The raster operation is the last stage of the pipeline and runs on the ROP units. This stage allows parameterised control over how the fragment shader's output is combined with the destination framebuffer. Although this stage does not support custom code execution and can only be controlled by parameterisation, as we shall see, it can be useful when combining fragment processor output with GPU memory.

#### 2.1.3 Textures

Textures are a key component in the programmer's arsenal when programming a GPU. Textures are blocks of memory which exist in off-chip device memory on the GPU card. They can be thought of as similar to bulk data arrays in a normal CPU programming environment. These blocks of memory consist of individual elements called *texels*, each of which has a storage format. An example of a texel's format could be a 4 wide FP32 vector representing the values for red, green, blue and alpha (RGBA). Traditionally textures were accessible only by the fragment processing stage in the GPU, allowing the combination of colours at particular locations within a texture and the colour values output by the rasteriser. DirectX 9 hardware improved texture access by supporting texture reads from both the vertex and fragment processors.

The fragment processor has a somewhat restricted ability to write to textures. This ability is termed as render-to-texture and is important in the context of general purpose processing. During the configuration of the pipeline, via OpenGL or DirectX, the programmer can specify that the fragment processor should output to a texture instead of a frame buffer. The advantage of rendering to texture is that the output of a pipeline pass can be used directly as the input of the next pipeline pass. Without render-to-texture, access to the output of the pipeline requires a copy-to-texture call, which involves the overhead of a memory copy (from frame buffer to texture). Iterative solutions, which require the consumption of the previous pipeline's output as the next pipeline's input can be implemented using a pair of textures, one for input and one for output.

A single texture cannot be used in this scenario due to coherence issues when reading and writing to the same texture in a single pass. After each pipeline pass the role of the texture pair is switched, the input texture becomes the output and vice versa. This implementation pattern is informally called the ping-pong technique [33].

Textures can be declared as 1, 2 or 3 dimensional, though 2 dimensional textures are most commonly used with DX9 GPUs. 1D textures are restrictive in size due to limits of 2048 texels per dimension. 3D texture write support is absent on some DX9 GPUs. Other DX9 GPUs support 3D texture writes, though inefficiently relative to 2D texture writes. The internal data types stored within a texel can be 16-bit or 32-bit floats and also a variety of bit width integers up to 16-bit. The number of data components stored per texel ranges from 1 to 4. It is a common technique to pack multiple data units into each texel to improve I/O efficiency and make effective use of the vector processors.

#### 2.1.4 General Purpose Computation

A problem that suits a parallel processing model can be broken into a large number of independent, or loosely bound tasks. The code which executes the task in this context is commonly referred to as a kernel. With regard to GPGPU, the kernel normally takes the form of a fragment shader which runs on fragment processors. To control the number of fragment shader instances, which can be seen as controlling the number of threads executing the kernel, we draw a 2D quadrilateral of size x pixels by y pixels. The aim of this draw command is to create  $x \times y$  number of fragments shader instances, corresponding to the number of fragments generated by the rasteriser. To ensure the size of the quadrilateral corresponds in a 1-to-1 manner with the number of generated fragments, we setup an orthogonal projection for the viewing volume which encompasses the quadrilateral. This type of projection preserves the dimensions of objects specified within the viewing volume. The viewing volume is a set of clipping planes which delimit 3D space and determine the active vertices which are sent to the vertex processors. We must also create a viewport with the same dimensions as the quadrilateral. The viewport is a plane onto which the viewing volume is projected. See Figure 2.3 for a depiction of the viewing volume, viewport and an orthogonal projection.

By configuring the graphics pipeline as described above we can create a defined number of threads which run on the GPU. To specify the input data made available to each fragment shader instance we can bind one or more 2D textures to the quadrilateral vertices. The rasteriser is responsible for interpolating the

Figure 2.3: Orthogonal projection configured to protect the co-ordinates of the input vertices.

texture co-ordinates bound to the vertices. These interpolated co-ordinates are made available to each fragment instance. A common requirement is to maintain a 1-1 mapping of fragment instances to input data elements. To achieve this the bound texture is made the same size as the quadrilateral, for example x by y as above. In the same way, the output can be stored following a 1-1 mapping between the fragment instances and output data elements by binding a texture of the same size as the quadrilateral to an output framebuffer object. These 1-1 mappings are useful when each thread's input and output data element count and size are symmetric. View volume, viewport and texture setup must be done to configure the graphics pipeline before a draw command is executed. The draw command triggers a single pass of the pipeline. It is equivalent to program execution, executing a potentially large number of fragment program instances and storing their output ready for readback by the CPU or for the next pass of the pipeline. Extensive coverage of general purpose computation on DX9 compliant GPUs and example applications can be found in the survey by Owens et al. [101].

#### 2.1.5 Restrictions and Performance Considerations

DX9 hardware is suited to the execution of data parallel tasks and lacks the flexibility of the standard CPU. We list the major restrictions and related performance considerations associated with using this hardware for general computation. Much of the information regarding DX9 restrictions can be found in Nvidia documentation [87, 107].

**Memory:** The DX9 GPU memory model provides a relatively complex and performance sensitive environment compared to the CPU. Care has to be taken with regard to memory usage to avoid performance bottlenecks. Points of note regarding the DX9 GPU's memory model include:

• The amount of high speed on-chip memory available for each ALU on a

DX9 GPU is limited to sizes within the estimated range of 16 KB to 24 KB. In comparison, a similar era CPU provides combined ALU access to much greater sizes of on-chip caches, typically in the order of 2-4 MB.

- The GPU's high speed memory mainly consists of a read-only cache for device memory, called the texture cache. Writing to device memory does not update the cache within a single pipeline pass. This causes cache coherence issues if fragment programs within a single pipeline pass read and write to the same memory locations.

- Vertex and fragment shaders have access to local read/write memory in the form of a limited set of temporary registers. These registers are the only form of fast on-chip read/write memory. Also of note, the registers do not support indexed access, limiting their use in certain contexts.

- Vertex and fragment shaders have access to read-only high speed on-chip constant registers. Like the temporary registers, these are limited in number. The numbers of available DX9 temporary and constant registers can be seen later in Table 2.1.

- Writing to device memory is supported only during the last stage of the rendering pipeline. A fragment shader cannot commit data to device memory at any stage, but can only output a limited amount of data to the raster operation stage which is responsible for committing values to device memory.

- The GPU lacks scatter support within its fragment processors. Output locations for data are determined via the pipeline configuration before pipeline execution and as such is fixed during fragment execution. The GPU can output to multiple textures, called render targets, however this is limited to 4 with DX9 GPUs. Thus, the amount of output generated by a single pipeline pass for a single fragment shader is limited to 4 texels.

- Memory allocation and memory free operations can only take place before or after a pipeline execution, but not during.

Thread Co-operation: The ALUs on the GPU, whether those within the vertex or fragment pipelines are incapable of sharing information during a single pass of the pipeline. The only manner of sharing data is to execute multiple pipeline passes using render-to-texture as described above. The execution of each pipeline pass comes with overheads not associated with core computation

and thus the more fine grained the requirement for data sharing, the less effective the GPU becomes.

Data Transfer: Any computation using a DX9 or DX10 GPU involves the transmission of data across the system bus. This data is not only input and output for shader execution but also any control operations related to pipeline configuration. The overhead of system bus use becomes more of a performance bottleneck as the amount of computation performed per pipeline pass decreases. Also, as previously mentioned, textures are used as data arrays for shader input and output. Thus, we transfer input and output data via texture transfers to and from the GPU. As we will see in Chapter 3, careful pipeline configuration is required to avoid large drops in transfer rate potential.

**Instruction Support:** The ALUs on DX9 GPUs support only 32-bit floating point for processing and data access. No native integer or bitwise operations are supported within the vertex and fragment processors. This reduces the effectiveness of the main source of GPU processing power with regards to cryptographic processing due to its heavy requirement for integer processing.

Branching Costs: Branching is supported on both the vertex and fragment processors. The vertex processors support MIMD (multiple instruction multiple data) branching, where each processor can execute a different thread of instructions. The fragment processors however act as a set of SIMD (single instruction multiple data) groups. If branching occurs within a SIMD group, each divergent path must be executed serially and the results predicated. Thus, although fragment processor branching is supported, there can be a large performance penalty if thread divergence is common.

**Program Length:** The vertex and fragment processors support a minimum of 512 static instructions as specified by the shader model specification. The number of actual executed instructions, i.e. dynamic instructions, is fixed at 65,535. These limitations restrict the complexity of the possible programs that can be run on the GPU in a single pass and as a result can lead to the fragmentation of programs into multiple parts, each called in a separate pipeline pass.

Access to Design Details: The finer details of the GPU architectures designed by vendors, Nvidia and AMD, are often kept secret. Information which may be beneficial to general purpose computation such as low level optimisation

can be difficult or impossible to access. Examples of this include the lack of information on the exact cache sizes available to each ALU or the rasterisation patterns used to generate fragments for handoff to the fragment processors. This tradition of secrecy continues with DX10 hardware.

Vertex Processors: Efficiently employing the vertex processors in a general purpose application can be difficult due to their placement and function within the graphics pipeline. Their output values are in the form of vertex attributes. These attributes are used by the fixed function rasteriser to generate the number of fragment shader instances required and also to generate each fragment's interpolated attribute values. The fixed interpolation of the vertex output attributes is beneficial in graphical applications, though has limited use in general computation. This interpolation can be avoided by using point primitives. However, this can result in idle fragment processors as the rasteriser will generate one fragment per vertex. DX10 hardware specifically addresses this issue by allowing more effective use of all the available GPU processors depending on the work required.

#### 2.2 DX10 Compliant Graphics Hardware

#### 2.2.1 Departure from DX9

The DirectX 10 specification details the system architecture for a more flexible programmable graphics processing unit. This specification requires a minimum feature set from compliant GPU's processing cores, which comes close to the flexibility of the traditional CPU. One of the main improvements in DX10 compliant hardware over DX9 in relation to cryptography is the addition of integer operation support. Included in the integer instruction set is support for arithmetic and bitwise operations. Another high profile change includes an increase in complexity of the graphics pipeline with an additional stage called the Geometry Shader. However, we will see in Section 2.2.3, that general purpose use of the GPU no longer has to be concerned with the graphics pipeline.

Shader model 4.0 [73] is included as part of the DX10 specification. The model specifies a unified instruction set for all of the programmable stages of the pipeline: vertex, fragment and geometry. The specification also defines a single virtual machine to be used as a common base for all programmable stages. These specification requirements have important implications for hardware implementations in terms of general purpose processing, see Section 2.2.2. Also included

Figure 2.4: Simplified block diagram of the GeForce 8800GTX, the first DX10 compliant GPU.

in the specification are large increases in the number of constant and temporary registers available to each programmable stage. These registers are now indexable, which increases their flexibility compared to previous register usage. Other improvements over DX9 include an increase in size of texture dimensions; increase in number of textures available to programmable stages; increase count of instruction slots, i.e. static program length; increased dynamic program length; new data load instruction to allow unfiltered device memory loads, rather than reading via texture sampling.

#### 2.2.2 Hardware Overview

As mentioned previously, the DX10 specification details both a common virtual machine base and instruction set for all programmable stages of the graphics pipeline. This is referred to as the unified shader model. Both Nvidia and AMD DX10 compliant GPUs reflect these requirements by implementing each programmable stage using the same processing cores. This approach is commonly known as unified shader architecture. The first commercially available DX10 compliant GPU was the Nvidia GeForce 8800GTX, an instance of the G8X [90] architecture family. This architecture provides an homogeneous array of processing cores. The GPU is capable of dynamically configuring the processing cores to assume the role of any of the three programmable stages, depending on the work required. As previously mentioned, it is difficult to make full use of the vertex processors for general purpose computation on DX9 GPUs. Both Nvidia and AMD DX10 compliant GPUs alleviate this issue by dynamically assigning the processing cores to the work type present in the pipeline.

#### 2.2.2.1 Nvidia DX10 Compliant Hardware

In Figure 2.4 we can see that the Geforce 8800GTX has 128 homogeneous stream processing (SP) cores. Each stream processor is a pipelined, in-order, scalar microprocessor capable of executing 32-bit floating point and 32-bit integer operations. The G8X and subsequent Nvidia architecture use scalar processors rather than the tradition vector processors found in graphics hardware. This is due to the realisation that as shader programs get more complex, the active vector width narrows [92, p27]. Thus, complex shader programs fail to fully utilize the entire width of the vector processors and as such leave hardware idle. A scalar approach does not suffer from this scenario. Also, as general purpose computations can commonly involve scalar operations, the full utilisation of vector hardware can require inventive data packing techniques. The change to scalar processors removes this obstacle to achieving performance on the GPU.

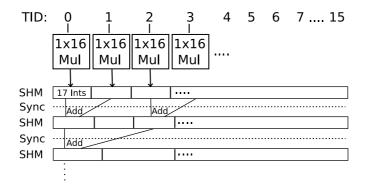

We can also see in Figure 2.4 that the stream processors are grouped into units called streaming multiprocessors (SM). Each SM contains 8 SPs; 2 special function units (SFU), which handle transcendental operations; a multithreaded instruction unit (MT IU); and shared memory. The SMs are grouped into pairs to form a thread processing cluster (TPC). Within a TPC the SMs share texture fetch units, texture addressing units, texture cache and other control logic. The architecture scales by a combination of changing the number of SPs per SM, SMs per TPC and the number of TPCs per GPU. The latest Nvidia architecture family at time of writing, the G200 [94], demonstrates this by increasing the processing cores to a total of 240 by combining 3 SMs per TPC and increasing the number of TPCs to 10. The design of the G200 is essentially the same as the original DX10 compliant GPU. In Figure 2.4 we also see the ROP layer, which serves the same purpose as in DX9 hardware. Also present is a level 2 cache (of undefined size) to provide increased performance for texture reads.

SIMT: As mentioned, an SM contains 8 SPs, which are tied to a multithreaded instruction unit. This arrangement functions in a manner called SIMT (single instruction, multiple-threads) [93], which is similar to SIMD. The SM is capable of executing threads, i.e. instances of a kernel execution, each of which run on a single SP. Each thread in effect executes with its own instruction pointer and register state. The similarity of SIMT to SIMD is that the instruction unit issues a single instruction for all SPs to execute at any one time. As such all SPs within an SM execute the same instructions, though can operate on their own unique data. The main difference between SIMT and SIMD is that SIMD instructions expose the vector width to software, whereas SIMT instructions are scalar and

Figure 2.5: Block diagram of the physical memory available to the SPs on a G8X GPU.

determine the execution and branch behaviour of a single thread. SIMT uses an abstraction that allows the SIMD like SM to create multiple independent scalar threads. This abstraction is implemented in hardware by a thread scheduler. The scheduler is capable of dynamically disabling the output of sets of ALUs within the SM during divergent thread execution.

Although the SM ensures correctness of execution of independent scalar threads, for efficiency it creates and schedules in groups of 32 parallel threads, called *warps*. This grouping of threads into warps is not reflected in software, though it is an important consideration in application development with regards to efficiency. The instruction unit issues the same instruction for each group of 32 threads, selectively committing results dependent on thread branching. With regard to performance, the architecture can be viewed as having an effective SIMD width of 32. The performance implications of thread branching on the architecture is discussed in Section 2.2.4.2.

**Memory:** All types of memory available to each stream processor can be seen in Figure 2.5. This figure shows all the on-chip, high speed memory and the off-chip memory available to each SP. Each memory type is designed for a specific task and generally requires explicit programmer instructions. Each physical memory type can be described as follows:

- Registers each SP has its own on-chip 32-bit register file.

- Shared Memory all SPs within a single SM share a small on-chip read-

/write memory. Shared memory can only be written to and read from during kernel execution and is accessibly only by the SPs that reside in the same SM as the shared memory.

- Constant Cache a read-only cache shared by all SPs that is used to speed up reads from constant memory space.

- Texture Cache a read-only cache shared by all SPs that is used to speed up reads from texture memory space. All memory read via the texture cache comes from the texture units within the TPC.

- Device Memory a read/write DRAM memory which exists off-chip. Whereas the on-chip memories are generally small, in the order of kilobytes, current graphics cards contain up to a low number of gigabytes of device memory.

Each SP within an SM has the ability to write to arbitrary locations within the GPU's device memory. This overcomes the DX9 fragment processor's lack of scatter support - the inability of shaders to write directly to device memory. This increases the DX10 GPU's flexibility with regard to general purpose computation. Also, SP access to shared memory has important synchronisation implications. Threads running on the same SM have the ability to co-ordinate via a synchronisation barrier instruction. Combining the synchronisation barrier with the high speed on-chip read/write shared memory can provide a means of implementing fine grained inter-thread co-operation.

#### 2.2.3 Programming Interface - CUDA

Both major GPU vendors have released new software environments for general purpose computation on their DX10 hardware. Nvidia released the Compute Unified Device Architecture (CUDA) [83] and ATI/AMD initially released "Close-To-Metal" (CTM) [1], which was later encapsulated in Stream SDK [2]. These new software environments allow programmers to avoid the use of traditional graphics APIs such as OpenGL and Direct3D to harness the GPU for general computation. All DX10 implementations within this thesis were made using CUDA and as such we focus on this architecture here. CUDA provides the ability to program the GPU using the C++ language with specialised extensions. These extensions can be grouped according to compute capability. Each GPU release that supports CUDA has a particular compute capability release number. The first CUDA supporting devices, and also the first DX10 compliant devices, implemented compute capability 1.0. Subsequent hardware releases

have followed with minor updates to the CUDA extensions and as such add new compute capability versions. At the time of writing, the latest CUDA compute capability was 1.3. The CUDA implementations presented in this thesis are based on compute capability 1.0 and thus, are compatible with all CUDA devices.

CUDA extends the C++ language to support the distinction of code which runs on the CPU and the GPU, called host and device code respectively. The CUDA compiler processes CUDA source files according to C++ syntax rules, however device code is restricted to a limited set of C++ syntax. Device and host code can be mixed within a single file, though are separated at the function level. A language extension provides function type qualifiers to indicate whether code runs on the host or device. A CUDA program which executes on the GPU is called a kernel. The "main" function, or starting point, for a kernel is specified by tagging a function with the <u>\_\_global\_\_</u> qualifier. A global function can only be called from a host function and can only call device functions. A \_device\_\_ qualifier can be used to denote a function which runs on the GPU and is callable from a global or another device function. A \_host\_ qualifier specifies a function which runs on the CPU and can be called by other host functions. Variable type qualifiers have also been added to the language and specify the type of memory that stores the variable. These qualifiers include \_\_device\_\_, \_\_constant\_\_ and \_\_shared\_\_. Texture memory is specified using its own type and registers are specified using automatic variables within device functions.

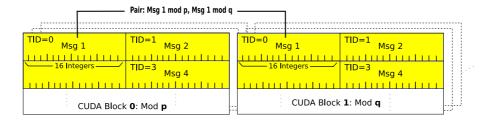

CUDA also provides a language extension to define the number of threads to be created on kernel execution. The number of threads are specified via the combination of a CUDA grid and a CUDA block. Threads are organised into blocks and blocks are organised into a grid. A block is represented by a 3 component vector, each component represents a dimension. The total number of threads in a block are derived from the multiplication of the three dimensions. All blocks within a grid are the same size. Also, all threads within a block execute on a single SM. A grid is represented by a 2 component vector, each component represents a dimension. The total number of blocks in a grid are derived from the multiplication of the two dimensions. The total number of threads spawned for a kernel execution on the GPU is derived from the number of threads per block multiplied by the number of blocks per grid. For example, given a CUDA block value of (1, 3, 100), and a CUDA grid value of (2, 3), the total number of threads for the kernel execution equals  $(1 \times 3 \times 100) \times (2 \times 3)$ . Note, that there is a hard limit of 512 threads per block, however we later discuss factors that can further restrict the number of threads per block.

Another language extension gives each thread access to a unique identifier via

Figure 2.6: Example of the CUDA execution model.

the use of CUDA's build-in threadIdx and blockIdx variables. The threadIdx variable is set to the threads position within the CUDA block it belongs to. The blockIdx is set to thread's block within the grid. The total number of threads executed on the GPU for a global function (kernel) call is equal to the number of threads per block multiplied by the number of blocks in the grid. A single C program running on the CPU can execute multiple, different kernels serially on the GPU. This technique can be used to isolate separate parallel and serial portions of a task, executing the serial parts on the CPU and the parallel parts on the GPU. Figure 2.6 illustrates an example of the execution of multiple kernels on the GPU, interleaved with serial code on the CPU. It also illustrates the grid and block configuration for each kernel execution.