## Quantum point contacts and resistive switching in Ni/NiO nanowire junctions

Sean M. Oliver, Jessamyn A. Fairfield, Allen T. Bellew, Sunghun Lee, James G. Champlain, Laura B. Ruppalt, John J. Boland, and Patrick M. Vora

Citation: Appl. Phys. Lett. 109, 203101 (2016); doi: 10.1063/1.4967502

View online: http://dx.doi.org/10.1063/1.4967502

View Table of Contents: http://aip.scitation.org/toc/apl/109/20

Published by the American Institute of Physics

## Quantum point contacts and resistive switching in Ni/NiO nanowire junctions

Sean M. Oliver, <sup>1</sup> Jessamyn A. Fairfield, <sup>2,3,a)</sup> Allen T. Bellew, <sup>2,3</sup> Sunghun Lee, <sup>2,3</sup> James G. Champlain, <sup>4</sup> Laura B. Ruppalt, <sup>4</sup> John J. Boland, <sup>2,3</sup> and Patrick M. Vora<sup>1,b)</sup>

<sup>1</sup>Department of Physics and Astronomy, George Mason University, Fairfax, Virginia 22030, USA

<sup>2</sup>School of Chemistry, Trinity College Dublin, Dublin, Ireland

<sup>3</sup>Centre for Research on Adaptive Nanostructures and Nanodevices (CRANN), Trinity College Dublin, Dublin, Ireland

<sup>4</sup>Naval Research Laboratory, Washington, District of Columbia 20375, USA

(Received 5 July 2016; accepted 30 October 2016; published online 14 November 2016)

Metal oxide devices that exhibit resistive switching are leading candidates for non-volatile memory applications due to their potential for fast switching, low-power operation, and high device density. It is widely accepted in many systems that two-state resistive behavior arises from the formation and rupture of conductive filaments spanning the oxide layer. However, means for controlling the filament geometry, which critically influences conduction, have largely been unexamined. Here, we explore the connection between filament geometry and conductance in a model resistive switching system based on the junction of two nickel/nickel oxide core/shell nanowires. Variable temperature current-voltage measurements indicate that either wide metallic filaments or narrow semiconducting filaments can be preferentially formed by varying the current compliance during electroformation. Metallic filaments behave as a conventional metallic resistance in series with a small barrier, while semiconducting filaments behave as quantum point contacts. The ability to tune filament geometry and behavior through the electroforming process may open avenues for enhanced functionality in nanoscale memristive systems. *Published by AIP Publishing*. [http://dx.doi.org/10.1063/1.4967502]

Materials that exhibit electrically induced resistive switching are naturally suited for robust and low-power non-volatile memory, where a bit is encoded in either a low (LRS) or high resistance state (HRS) and read out non-destructively. Many implementations of this concept are based on a thin-film dielectric sandwiched between metal contacts. After an initial electroforming process, application of an electric field switches the device's electrical conductivity between a LRS and a HRS. Devices based on transition metal oxides, such as NiO<sub>x</sub>, <sup>2-4</sup> TiO<sub>x</sub>, <sup>4,5</sup> HfO<sub>x</sub>, <sup>6</sup> Ta<sub>2</sub>O<sub>5</sub>, <sup>5,7,8</sup> and SiO<sub>x</sub>, <sup>9,10</sup> have all demonstrated resistive switching with some devices exhibiting resistance ratios and cycling endurances sufficient for many computational memory applications. <sup>9,11–16</sup>

Resistive switching in oxide-based systems is thought to arise from the rupture and reformation of nanoscale conducting filaments that span the oxide. 1,4,13,17-19 A fully formed, intact filament yields the conductive LRS, while a ruptured filament leads to the HRS. These filaments are composed of a chain of oxygen vacancies, with rupture and reformation induced by either electric field- or Joule-heating-induced vacancy migration. 1,4,20-23 Initial formation of the conductive filament from the pristine oxide requires application of a large electric field that triggers a soft breakdown of the dielectric. 4,21,24,25 Typically, filamentary conduction is viewed as an all-or-nothing response, where either metallic

(LRS) or insulating (HRS) behavior occurs. While sufficient for basic memory applications, the ability to achieve electronic states beyond these two regimes is desirable both for fundamental investigations of filamentary conduction, as well as device applications.

In this work, we demonstrate a semiconducting LRS, in addition to the typically observed metallic LRS and insulating HRS, by varying the electroformation process in a model resistive switching system based on the junction between two Ni/NiO core/shell nanowires. 12,21,26,27 While prior studies have explored the impact of electroformation on device performance, 4,23,28,29 in this work, we present a comprehensive examination of the temperature-dependent electrical characteristics arising from different formation procedures. Based on current-voltage (IV) and temperature-dependent resistance (R(T)) data, the metallic LRS behaves as a conventional metallic resistance in series with a small barrier, while the semiconducting LRS behaves as an atomically thin quantum point contact (QPC). 30-35 QPC conduction has been previously observed in HfO<sub>2</sub> devices, <sup>34,36</sup> but has not been documented in NiO systems. These observations suggest that the metallic (semiconducting) LRS derives from wide (narrow) filament constrictions that are preferentially achieved by executing either a single- or multi-step electroformation process. Tuning the filament geometry, and thus the conduction characteristics, therefore introduces an additional variable for functionality in nanoscale memristive devices.

Ni nanowires  $\sim$ 35 nm in diameter and  $\sim$ 10 to 20  $\mu$ m in length were purchased from a commercial supplier (Nanomaterials.it), drop-cast onto Si/SiO<sub>2</sub> substrates, and

b) Author to whom correspondence should be addressed. Electronic mail: pvora@gmu.edu

a)Present address: School of Physics, National University of Ireland Galway, University Road, Galway, Ireland.

oriented by a magnetic field. A second drop-cast was performed in an orthogonal field angle, resulting in crossed nanowire junctions. Scanning electron microscope (SEM) images of a device are shown in the inset of Figure 1(a). The NiO layer is self-limited and ~4 to 8 nm thick, yielding ~8 to 16 nm separation between conducting Ni cores. Electrodes were then patterned via electron beam lithography, with 5 nm of Ti and 150 nm of Au deposited using electron beam evaporation. Devices were loaded into a Lake Shore CRX-VF cryogenic probe station for temperature-dependent electrical characterization. All measurements were performed in vacuum using a Keithley 4200-SCS Parameter Analyzer and were taken at temperatures from 15 to 300 K, with 10 consecutive scans averaged at each temperature.

To achieve varying LRSs of the nanowire junctions, two electroformation procedures were performed at 300 K in vacuum by applying a voltage sweep with different current compliances (I<sub>CC</sub>). We note that filament formation can occur at the Au-NiO interface as well as the nanowire junction and that, in principle, there is potentially confusion regarding the location of the filament dominating conduction. 26,27 However, the contact area at the nanowire junction is reduced due to the junction geometry as well as the surface roughness of the nanowires (Figure S1 of supplementary material) when compared to the Au-NiO interface, while the oxide is twice as thick at the junction. These structural properties imply that filaments will be the last to form in the junction and that these filaments will dominate transport characteristics. This was confirmed by comparing two- vs four-terminal devices (where the contacts with the leads can be formed independently) and no observable difference was found. The first formation procedure (Figure 1(a)) used a dual sweep with  $I_{CC} = 10 \,\mu\text{A}$  in voltage steps of 0.025 V (black trace). The dramatic reduction in resistance at  $\sim 5.1 \, \text{V}$  indicates filament formation, resulting in a "metallic" LRS based on the low resistance (4.79 k  $\Omega$  at 0.8 V at 300 K), the linear IV relation at room temperature (Figure 3(a)), and positive temperature coefficient of resistance (TCR). Figure 1(b) shows the second electroformation procedure where four formation sweeps were performed,

starting with  $I_{CC} = 0.1 \,\mu\text{A}$ , and increasing by one order of magnitude in subsequent sweeps to end with  $I_{CC} = 100 \,\mu\text{A}$ . The resulting filament exhibits a "semiconducting" LRS, characterized by non-linear IVs, higher resistance (179 k  $\Omega$ at 0.8 V at 300 K), and negative TCR. Subsequent RESET (switching from LRS to HRS) and SET (switching from HRS to LRS) operations occurred at positive bias (unipolar switching), and were reproducible over at least 10 cycles, as shown in Figure 1(c) for a semiconducting LRS. We note that the RESET voltage is larger than the SET voltage in the semiconducting case which is the reverse of prior observations in other NiO resistive switching systems.<sup>23</sup> This behavior has been observed in  $SiO_x^{37,38}$  as well as in devices constructed from ZnO microwires.<sup>39</sup> In the latter case, the authors also observed a reversal of SET and RESET voltages compared to bulk ZnO. We speculate that in our system the reversal of SET and RESET voltages originates from the unique transport characteristics of the QPC, but further study and modeling is required to confirm this.

The electroformation procedures shown in Figures 1(a) and 1(b) preferentially lead to metallic or semiconducting states, respectively. However, since breakdown is a stochastic process, linear or non-linear characteristics can occur with either method. We formed 16 devices using the singlestep method in Figure 1(a) and found that 8 devices broke during the electroformation, 3 devices exhibited predominantly linear IV characteristics, and 5 displayed non-linear IV behaviors. The multi-step procedure in Figure 1(b) was also used on 16 devices and led to non-linear IVs in 8 cases, linear IVs in 5 cases, and 3 ruptured devices during the electroformation process. Non-linear characteristics are preferentially achieved with the procedure in Figure 1(b); however, our observations do suggest that there is a degree of randomness in the electroformation process that likely depends on the rate of current increase.

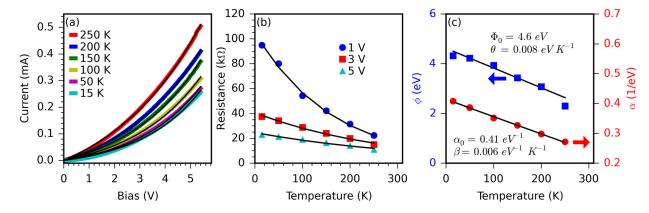

While the majority of experimental studies on resistive switching devices have been performed at room temperature, variable temperature measurements can illuminate the mechanism of filamentary conduction. IV characteristics of the semiconducting LRS generated with the multi-step

FIG. 1. (a) Formation of a metallic LRS (red trace) in a nanowire junction using a single electroformation sweep (black trace) with a current compliance of  $10\,\mu\text{A}$ . Inset shows a device schematic illustrating the nanowire junction. (b) Formation of a semiconducting LRS using a series of electroformation sweeps with progressively higher current compliances, beginning at  $0.1\,\mu\text{A}$  and increasing to  $100\,\mu\text{A}$ . The numbers 1–4 reference measurement order. (c) Forward IV sweeps demonstrating repeated unipolar switching between the semiconducting LRS and the HRS for 10 SET/RESET cycles. The inset compares the resistance of the LRS (red squares) to that of the HRS (black squares) over the switching cycles depicted.

electroformation procedure of Figure 1(b) were measured at selected temperatures from 15 K to 250 K and are plotted in Figure 2. The IV relations are nonlinear over the entire bias range (Figure 2(a)) while the R(T) data exhibit a negative TCR (Figure 2(b)), both of which are consistent with semiconducting transport. Interestingly, though most semiconducting LRSs measured were stable with switching (Figure 1(c)), one device exhibited considerable modification of its IV curves in a different RESET/SET cycle, which is discussed in the supplementary material in Figures S2 and S3.

Non-linear IV characteristics in filamentary conductors have been attributed to a variety of mechanisms, including Poole-Frenkel conduction, thermionic emission, and tunneling. 19,24,40-43 R(T) data demonstrated by the conventional semiconducting LRS (Figure 2(b)) follow an exponential form,  $R \propto \exp(-aT)$ , at odds with the expected temperature dependence of each of the above. 44 However, this behavior is in good agreement with the temperature trends predicted by the QPC model, which describes conduction through an atomically thin bottleneck constriction. 31,32,35 In this framework, quantum confinement at the constriction results in a local potential barrier, commonly modeled as parabolic in shape, and a series of energy subbands where conduction occurs only through the lowest level.<sup>35</sup> The temperaturedependent IV relationship for a QPC with a single conducting channel is given by<sup>31</sup>

$$I(V,T) = \frac{2e}{\alpha h} \left\{ \frac{\exp(-\alpha \left[\Phi(T) - \gamma eV\right])}{\operatorname{sinc}(\pi \alpha k T)} \left[1 - \exp(-\alpha eV)\right] \right\},\tag{1}$$

where e is the electron charge, h is Planck's constant, k is Boltzmann's constant,  $\gamma$  is a coupling factor between the external field and the local potential,  $\alpha$  is related to the inverse of the potential barrier curvature, and  $\Phi(T)$  is the effective barrier height. This barrier is temperature dependent,  $\Phi(T) = \Phi_o - \theta T$ , where  $\Phi_o$  is the 0 K effective barrier height and the slope  $\theta$  describes the reduction of barrier height due to increasing atomic vibrations at elevated temperatures. The result is a current, and thus a resistance, that varies exponentially with temperature,  $I(T) \propto \exp\left(-\alpha[\Phi_o - \theta T]\right)$ . As described by Walczyk  $et\ al.$ ,  $\gamma = \frac{x}{t_{ox}}$ , where x is the location of the filament constriction as measured from the carrier-

injecting (cathodic) nanowire and  $t_{ox}$  is the oxide thickness.<sup>31</sup> In NiO thin films, it is suggested that conducting filaments grow from the cathode to the anode, <sup>4</sup> so we expect the filament constriction to be located within the oxide of the anodic nanowire. Using  $\gamma=1$ , we find that the data in Figure 2(a) is fit well by the QPC model over the entire temperature and voltage range (black traces of Figures 2(a) and 2(b)), with the extracted values of  $\Phi(T)$  and  $\alpha$  summarized in Figure 2(c). Our fits indicate a 0 K barrier of  $\Phi_o=4.6\,eV$  and slight temperature dependence in the barrier curvature, as well, with  $\alpha$  following the functional form  $\alpha=\alpha_o-\beta T$ .

If the barrier  $\Phi(T)$  is known, the radius of the filament constriction at its narrowest point can be estimated through the following equation:<sup>34</sup>

$$r = \frac{hz_0}{2\pi\sqrt{2m^*\Phi(T)}}. (2)$$

Here,  $z_0 = 2.404$  is the first zero of the Bessel function and  $m^*$  is the electron effective mass. For NiO,  $m^*$  has been found to vary between 0.6  $m_0$  and  $m_0$ , where  $m_0$  is the free electron mass. Assuming  $m^* = 0.8m_0$ , and using the results from the analysis of  $\Phi(T)$  and  $\alpha$  in Figure 2(c), we estimate the radius of the filament in the semiconducting LRS to be 2.5–3.5 Å, roughly corresponding to 1–2 Ni atoms thick.

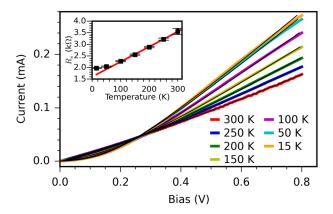

Temperature-dependent IV measurements taken on a device set into a metallic LRS using the single-step electroformation procedure of Figure 1(a) are plotted in Figure 3, where the bias was kept below 1 V to avoid resetting the device into a HRS. The IVs reveal two bias regimes that exhibit opposite temperature-dependent behaviors, with a transition at  $\sim$ 0.27 V. All IV curves are linear in the high bias regime with a positive TCR, while those in the low bias regime are nonlinear with a negative TCR.

Unlike the semiconducting LRS, the metallic LRS could not be fit by the QPC model in Eq. (1). In fact, the intersection of the IV curves at 0.27 V is difficult to capture with a model that contains only one conduction mechanism and therefore we require two competing mechanisms to account for the observed behavior. Such intersecting IVs are consistent with conduction in a system where small, inhomogeneous barriers are in series with a conventional metallic resistance: 46,47 low-field, low-temperature behavior is dominated by conduction

FIG. 2. (a) Temperature-dependent nonlinear IV measurements for a device in the semiconducting LRS formed using the electroformation procedure described in Figure 1(b). (b) R(T) data extracted from (a) at three different voltages. The black traces in (a) and (b) are fits to the QPC model. (c) Extracted parameters  $\Phi$  and  $\alpha$  obtained from QPC model fits to the semiconducting LRS data in (a) and (b). The black lines show the linear fits  $\Phi(T) = \Phi_o - \theta T$  and  $\alpha = \alpha_0 - \beta T$ .

FIG. 3. Temperature-dependent IV curves for a device in the metallic LRS formed using the electroformation procedure described in Figure 1(a). The black traces are fits to Eq. (3). Inset: Temperature-dependent series resistance  $R_s(T)$  extracted from fits to Equation (3). The error bars represent a 95% confidence interval.

across the barrier, and high-field, high-temperature conduction is dictated by the series resistance. Therefore, we propose that the single, high-compliance-current formation step generates a spatially non-uniform filament between the Ni nanowire cores. While the filament is sufficiently wide to prevent quantization effects, at some point along its length exists a small potential barrier to conduction. Outside of this barrier, the remainder of the metallic filament and the Ni nanowire cores contribute a series resistance that decreases with decreasing temperature, giving rise to the intersecting IV behavior observed in Figure 3. The IV relationship for this system is given by the relation

$$I(V,T) = A\left(\exp\left(\frac{e[V - IR_s(T)]}{nkT}\right) - 1\right),\tag{3}$$

where A is a temperature-dependent current prefactor,  $R_s(T)$  is the series resistance, and n is a temperature-dependent ideality factor. The data fit this equation well (black traces of Figure 3) and allow for the extraction of  $R_s$  at each temperature (Figure 3, inset).  $R_s(T)$  is linear above 50 K (red trace of Figure 3, inset), yielding a positive TCR of  $\sim 2.2 \times 10^{-3}$  K<sup>-1</sup>, which is consistent with recent observations by Iwata et~al. in the LRS of NiO film devices. The temperature dependence of the parameters A and n can be found in Figure S4 of the supplementary material.

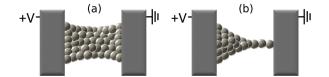

The variation in temperature-dependent conduction between the two LRSs suggests a path toward control of the filament geometry through the electroformation procedure. The single-step, high I<sub>CC</sub> process of Figure 1(a) generated a thick filament in series with a spatially inhomogeneous potential barrier that exhibits metallic conduction in the LRS (Figure 4(a)), while the stepped  $I_{CC}$  electroformation procedure in Figure 1(b) yielded a filament with an atomic constriction that exhibits QPC-like semiconducting behavior in the LRS (Figure 4(b)). Evidence suggests that switching from either the metallic or semiconducting LRS into a HRS results from an actual rupture of the filament, where conduction occurs through a series of larger, randomly distributed potential barriers. 4,21,48 In these devices, the HRS shows a very high resistance and variable temperature-dependent IV characteristics (Figure S5 of supplementary material).

FIG. 4. Schematics of (a) a wide metallic filament formed using a singlestep electroformation sweep and (b) a narrow semiconducting filament formed using a stepped electroformation procedure.

In conclusion, we have demonstrated the realization of metallic and semiconducting LRSs in nominally identical Ni/ NiO single nanowire junctions. Distinct filamentary structures and electrical behaviors can be achieved by regulating the current compliance during the electroformation step. In particular, a series of sweeps with gradually increasing compliances preferentially leads to a narrow filament with semiconducting characteristics that are well fit using the QPC model for electronic transport through an atomic scale constriction. The variety of filamentary conductive states demonstrates the potential of Ni nanowire junctions for use as multifunctional nanoscale memory devices and as a platform for investigating quantum transport in the one-dimensional limit. We envision that the ability to tune filament geometry through the electroformation process can be made deterministic with additional device engineering and may lead to the on-demand realization of semiconducting or metallic behavior. The ability to control the conducting state in filamentary systems would be potentially useful for combining selector and memristor functionalities in a single device and could also support advanced neuromorphic architectures that benefit from a diversity of device behaviors.

See supplementary material for a transmission electron microscopy image of a Ni/NiO nanowire, further discussion of the semiconducting LRS, temperature dependence of the extracted parameters from fitting to the metallic LRS, and temperature-dependent IV curves of the HRS.

P.M.V. and S.M.O. acknowledge the support from the Office of Naval Research through Grant No. N-00014-15-1-2357 and from the GMU Presidential Scholarship Program. J.A.F., A.T.B., S.L., and J.J.B. wish to acknowledge the support from the AMBER Centre and Advanced Microscopy Laboratory, as well as funding from the European Research Council under Advanced Grant No. 321160.

<sup>&</sup>lt;sup>1</sup>R. Waser and M. Aono, Nat. Mater. 6, 833 (2007).

<sup>&</sup>lt;sup>2</sup>S. Seo, M. J. Lee, D. H. Seo, E. J. Jeoung, D. S. Suh, Y. S. Joung, I. K. Yoo, I. R. Hwang, S. H. Kim, I. S. Byun, J. S. Kim, J. S. Choi, and B. H. Park, Appl. Phys. Lett. **85**, 5655 (2004).

<sup>&</sup>lt;sup>3</sup>P. N. Nirmalraj, A. T. Bellew, A. P. Bell, J. A. Fairfield, E. K. McCarthy, C. O'Kelly, L. F. C. Pereira, S. Sorel, D. Morosan, J. N. Coleman, M. S. Ferreira, and J. J. Boland, Nano Lett. **12**, 5966 (2012).

<sup>&</sup>lt;sup>4</sup>K. M. Kim, D. S. Jeong, and C. S. Hwang, Nanotechnology **22**, 254002 (2011).

<sup>&</sup>lt;sup>5</sup>M. Terai, Y. Sakotsubo, S. Kotsuji, and H. Hada, IEEE Electron Device Lett. 31, 204 (2010).

<sup>&</sup>lt;sup>6</sup>J. S. Lee, S. Lee, and T. W. Noh, Appl. Phys. Rev. 2, 31303 (2015).

<sup>&</sup>lt;sup>7</sup>G. Wang, J.-H. Lee, Y. Yang, G. Ruan, N. D. Kim, Y. Ji, and J. M. Tour, Nano Lett. **15**, 6009 (2015).

<sup>&</sup>lt;sup>8</sup>P. R. Mickel, A. J. Lohn, B. Joon Choi, J. Joshua Yang, M. X. Zhang, M. J. Marinella, C. D. James, and R. S. Williams, Appl. Phys. Lett. **102**, 223502 (2013).

- <sup>9</sup>S. H. Jo and W. Lu, Nano Lett. **8**, 392 (2008).

- <sup>10</sup>M. Buckwell, L. Montesi, S. Hudziak, A. Mehonic, and A. J. Kenyon, Nanoscale 7, 18030 (2015).

- <sup>11</sup>S. H. Jo, K. H. Kim, and W. Lu, Nano Lett. 9, 870 (2009).

- <sup>12</sup>A. T. Bellew, A. P. Bell, E. K. McCarthy, J. A. Fairfield, and J. J. Boland, Nanoscale 6, 9632 (2014).

- <sup>13</sup>L. Goux, J. G. Lisoni, X. P. Wang, M. Jurczak, and D. J. Wouters, IEEE Trans. Electron Devices **56**, 2363 (2009).

- <sup>14</sup>S. Otsuka, Y. Hamada, T. Shimizu, and S. Shingubara, Appl. Phys. A 118, 613 (2015).

- <sup>15</sup>J. J. Yang, M. X. Zhang, J. P. Strachan, F. Miao, M. D. Pickett, R. D. Kelley, G. Medeiros-Ribeiro, and R. S. Williams, Appl. Phys. Lett. 97, 232102 (2010).

- <sup>16</sup>M.-J. Lee, C. B. Lee, D. Lee, S. R. Lee, M. Chang, J. H. Hur, Y.-B. Kim, C.-J. Kim, D. H. Seo, S. Seo, U.-I. Chung, I.-K. Yoo, and K. Kim, Nat. Mater. 10, 625 (2011).

- <sup>17</sup>D. Ielmini, F. Nardi, C. Cagli, and A. L. Lacaita, IEEE Electron Device Lett. 31, 353 (2010).

- <sup>18</sup>B. Magyari-Köpe, M. Tendulkar, S.-G. Park, H. D. Lee, and Y. Nishi, Nanotechnology 22, 254029 (2011).

- <sup>19</sup>D. Ielmini, F. Nardi, and C. Cagli, Nanotechnology **22**, 254022 (2011).

- <sup>20</sup>S. Tang, F. Tesler, F. G. Marlasca, P. Levy, V. Dobrosavljević, and M. Rozenberg, Phys. Rev. X 6, 011028 (2016).

- <sup>21</sup>D. C. Kim, S. Seo, S. E. Ahn, D.-S. Suh, M. J. Lee, B.-H. Park, I. K. Yoo, I. G. Baek, H.-J. Kim, E. K. Yim, J. E. Lee, S. O. Park, H. S. Kim, U.-I. Chung, J. T. Moon, and B. I. Ryu, Appl. Phys. Lett. 88, 202102 (2006).

- <sup>22</sup>L. Goux, J. G. Lisoni, M. Jurczak, D. J. Wouters, L. Courtade, and C. Muller, J. Appl. Phys. **107**, 24512 (2010).

- <sup>23</sup>D. Ielmini, Semicond. Sci. Technol. **31**, 63002 (2016).

- <sup>24</sup>K. Jung, H. Seo, Y. Kim, H. Im, J. Hong, J. W. Park, and J. K. Lee, Appl. Phys. Lett. **90**, 052104 (2007).

- <sup>25</sup>I. K. Yoo, M. J. Lee, D. H. Seo, and S. J. Kim, Appl. Phys. Lett. **104**, 222902 (2014).

- <sup>26</sup>L. He, Z. M. Liao, H. C. Wu, X. X. Tian, D. S. Xu, G. L. W. Cross, G. S. Duesberg, I. V. Shvets, and D. P. Yu, Nano Lett. 11, 4601 (2011).

- <sup>27</sup>C. Cagli, F. Nardi, B. Harteneck, Z. Tan, Y. Zhang, and D. Ielmini, Small 7, 2899 (2011).

- <sup>28</sup>G.-H. Buh, I. Hwang, and B. H. Park, Appl. Phys. Lett. **95**, 142101 (2009).

- <sup>29</sup>J. Joshua Yang, F. Miao, M. D. Pickett, D. A. A. Ohlberg, D. R. Stewart, C. N. Lau, and R. S. Williams, Nanotechnology 20, 215201 (2009).

- <sup>30</sup>E. A. Miranda, C. Walczyk, C. Wenger, and T. Schroeder, IEEE Electron Device Lett. 31, 609 (2010).

- <sup>31</sup>C. Walczyk, D. Walczyk, T. Schroeder, T. Bertaud, M. Sowińska, M. Lukosius, M. Fraschke, D. Wolansky, B. Tillack, E. Miranda, and C. Wenger, IEEE Trans. Electron Devices 58, 3124 (2011).

- <sup>32</sup>A. Avellán, E. Miranda, D. Schroeder, and W. Krautschneider, J. Appl. Phys. 97, 14104 (2005).

- <sup>33</sup>X. Lian, X. Cartoixà, E. Miranda, L. Perniola, R. Rurali, S. Long, M. Liu, and J. Suñé, J. Appl. Phys. **115**, 244507 (2014).

- <sup>34</sup>L. M. Procel, L. Trojman, J. Moreno, F. Crupi, V. Maccaronio, R. Degraeve, L. Goux, and E. Simoen, J. Appl. Phys. 114, 74509 (2013).

- <sup>35</sup>E. Miranda and J. Sune, in 2001 IEEE International Reliability Physics Symposium Proceedings. 39th Annual (Cat. No.00CH37167) (IEEE, 2001), pp. 367–379.

- <sup>36</sup>J. Sune, S. Long, C. Cagli, L. Perniola, X. Lian, X. Cartoixa, R. Rurali, E. Miranda, D. Jimenez, and M. Liu, in *ICSICT 2012 IEEE 11th International Conference on Solid-State Integrated Circuit Technology Proceedings* (IEEE, 2012), pp. 1–4.

- <sup>37</sup>J. Yao, Z. Sun, L. Zhong, D. Natelson, and J. M. Tour, Nano Lett. 10, 4105 (2010).

- <sup>38</sup>Y. F. Chang, B. Fowler, Y. C. Chen, Y. T. Chen, Y. Wang, F. Xue, F. Zhou, and J. C. Lee, J. Appl. Phys. 116, 043708 (2014).

- <sup>39</sup>Y. Huang, Y. Luo, Z. Shen, G. Yuan, and H. Zeng, Nanoscale Res. Lett. 9, 381 (2014).

- <sup>40</sup>J. J. Yang, D. B. Strukov, and D. R. Stewart, Nat. Nanotechnol. **8**, 13 (2012).

- <sup>41</sup>E. Miranda and J. Suñé, Microelectron. Reliab. 44, 1 (2004).

- <sup>42</sup>R. Fang, W. Chen, L. Gao, W. Yu, and S. Yu, IEEE Electron Device Lett. **36**, 567 (2015).

- <sup>43</sup>F. Hernandez-Ramirez, A. Tarancon, O. Casals, E. Pellicer, J. Rodriguez, A. Romano-Rodriguez, J. R. Morante, S. Barth, and S. Mathur, Phys. Rev. B: Condens. Matter Mater. Phys. 76, 085429 (2007).

- <sup>44</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed. (John Wiley & Sons, Inc., 2007).

- <sup>45</sup>M. D. Irwin, J. D. Servaites, D. B. Buchholz, B. J. Leever, J. Liu, J. D. Emery, M. Zhang, J. H. Song, M. F. Durstock, A. J. Freeman, M. J. Bedzyk, M. C. Hersam, R. P. H. Chang, M. A. Ratner, and T. J. Marks, Chem. Mater. 23, 2218 (2011).

- <sup>46</sup>S. Chand, Semicond. Sci. Technol. **19**, 82 (2004).

- <sup>47</sup>J. Osvald, Solid State Commun. **138**, 39 (2006).

- <sup>48</sup>T. Iwata, Y. Nishi, and T. Kimoto, J. Appl. Phys. 117, 225701 (2015).