## LEABHARLANN CHOLÁISTE NA TRÍONÓIDE, BAILE ÁTHA CLIATH Ollscoil Átha Cliath

## TRINITY COLLEGE LIBRARY DUBLIN The University of Dublin

#### Terms and Conditions of Use of Digitised Theses from Trinity College Library Dublin

#### **Copyright statement**

All material supplied by Trinity College Library is protected by copyright (under the Copyright and Related Rights Act, 2000 as amended) and other relevant Intellectual Property Rights. By accessing and using a Digitised Thesis from Trinity College Library you acknowledge that all Intellectual Property Rights in any Works supplied are the sole and exclusive property of the copyright and/or other IPR holder. Specific copyright holders may not be explicitly identified. Use of materials from other sources within a thesis should not be construed as a claim over them.

A non-exclusive, non-transferable licence is hereby granted to those using or reproducing, in whole or in part, the material for valid purposes, providing the copyright owners are acknowledged using the normal conventions. Where specific permission to use material is required, this is identified and such permission must be sought from the copyright holder or agency cited.

#### Liability statement

By using a Digitised Thesis, I accept that Trinity College Dublin bears no legal responsibility for the accuracy, legality or comprehensiveness of materials contained within the thesis, and that Trinity College Dublin accepts no liability for indirect, consequential, or incidental, damages or losses arising from use of the thesis for whatever reason. Information located in a thesis may be subject to specific use constraints, details of which may not be explicitly described. It is the responsibility of potential and actual users to be aware of such constraints and to abide by them. By making use of material from a digitised thesis, you accept these copyright and disclaimer provisions. Where it is brought to the attention of Trinity College Library that there may be a breach of copyright or other restraint, it is the policy to withdraw or take down access to a thesis while the issue is being resolved.

#### **Access Agreement**

By using a Digitised Thesis from Trinity College Library you are bound by the following Terms & Conditions. Please read them carefully.

I have read and I understand the following statement: All material supplied via a Digitised Thesis from Trinity College Library is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of a thesis is not permitted, except that material may be duplicated by you for your research use or for educational purposes in electronic or print form providing the copyright owners are acknowledged using the normal conventions. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone. This copy has been supplied on the understanding that it is copyright material and that no quotation from the thesis may be published without proper acknowledgement.

## **FPGA** based solver for Internet Eigenvectors

Séamas McGettrick

A thesis submitted to the University of Dublin in partial fulfilment of the requirements of the degree of Doctor of Philosophy

School of Engineering,

Department of Mechanical and Manufacturing Engineering,

University of Dublin, Trinity College.

9430

### **Declaration**

I declare that the work described in this thesis is, unless otherwise stated, entirely my own work and has not been submitted as an exercise for a degree at this or any other University. I agree that Trinity College Library may lend or copy this thesis upon request.

Signature of author:

Séamas McGettrick

May 2009

### **Abstract**

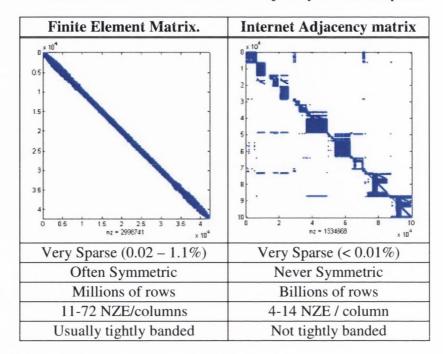

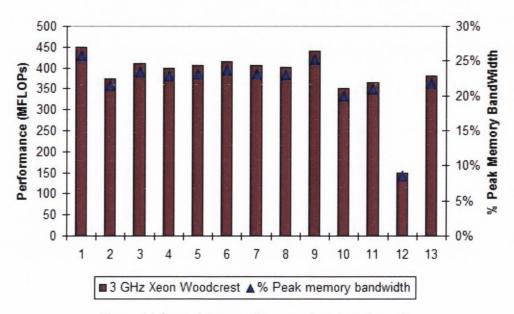

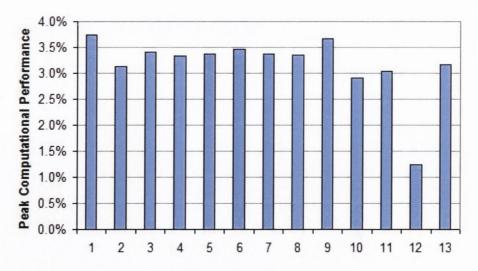

Calculating an Internet Eigenvector for Internet ranking is a massive computational problem dominated by Sparse Matrix by Vector Multiplication (SMVM) where the matrix is very sparse, unsymmetrical and unstructured. The computation presents a serious challenge to general purpose processors (GPP) on which it is run. The GPP only achieves a fraction of its peak performance. The result of this is a very lengthy computation time.

Specialised hardware running on FPGAs has been used in other scientific applications to accelerate algorithms where very sparse SMVM is required. This thesis attempts to apply the knowledge gained, from using FPGAs on these other scientific calculations, to PageRank - the most popular Internet ranking algorithm - for the first time.

This is done firstly by implementing and benchmarking two floating point hardware architectures (SPAR and SCAR) designed for finite element analysis against a state of the art GPP. Two variations of the SCAR SMVM unit are presented. One of which has a single MAC pipeline and the second which has a dual MAC pipeline and thus fully utilises the available memory bandwidth. A third architecture is proposed and implemented which is designed to work especially with the PageRank algorithm. Two variations of this hardware architecture are also created, one that has three SMVM units with 1024 vector entries in the X and Y cache and the other which has two SMVM units with 2048 vector words stored in the cache. The five variations of the hardware architecture are targeted to a Virtex-II V6000 FPGA with four independent memory channels.

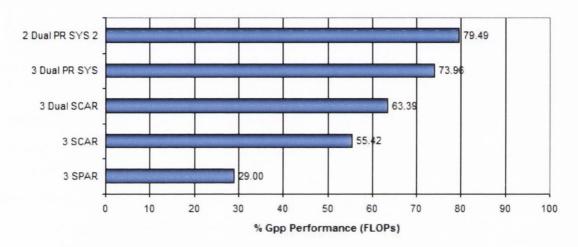

With the exception of the SPAR architecture, all of the FPGA based architectures achieved over 50% of the performance of the GPP despite having a clock rate of

about 100 MHz which is 30 times slower than the 3 GHz clock rate of the GPP. The DDR-266 SDRAMS used by the FPGA are also less than half the speed of the DDR2-667 SDRAM modules used in the GPP. The Specialised PageRank hardware with two SMVM units and 2048 Vector entries in its cache is the highest performing FPGA architecture achieving approximately 80% of the GPP performance.

The FPGA architectures pad their streams with NOPs to avoid Read After Write (RAW) hazards in the adders. NOPS inserted to avoid RAW hazards account for between 12% and 16% of the matrix stream length. It is shown that the number of RAW hazards is directly proportional to adder latency and so reducing adder latency should reduce NOPs in the stream. One method to reduce adder latency is to reduce precision. Thus, a number of tests are presented to estimate the precision needed to calculate the PageRank algorithm and two of the above systems are implemented using fixed point arithmetic. The performance of the fixed point implementations is only marginally better than the floating point implementations. This is due to the SMVM being only part of the PageRank algorithm.

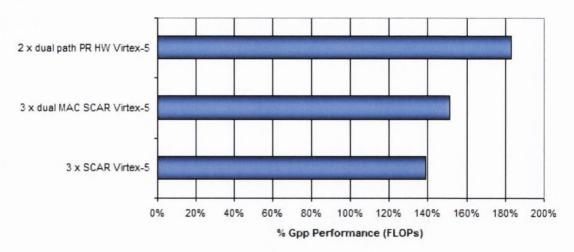

Finally the two best performing designs are targeted at a Virtex-5 FPGA with the result that the generic SMVM architecture performs on average about 1.5 times faster than the GPP and the specialised PageRank HW can run at about 1.8 times the speed of the GPP even though the clock rate is 14 times slower than that of the GPP.

Throughout the thesis a number of limitations of the architectures are discussed together with suggested improvements that could be made to the architectures in future implementations of a hardware solver for Internet Eigenvectors.

### **Publications Associated with the Thesis**

- [16] S. McGettrick, D. Geraghty, and C. McElroy, "Searching the Web with an FPGA Based Search Engine," in Reconfigurable Computing: Architectures, Tools and Applications, Brazil, 2007, pp. 350-357.

- [17] D. Gregg, C. Mc Sweeney, C. McElroy, F. Connor, S. McGettrick, D. Moloney, and D. Geraghty, "FPGA Based Sparse Matrix Vector Multiplication using Commodity DRAM Memory," in Field Programmable Logic and Applications, 2007. FPL 2007. International Conference on, 2007, pp. 786-791.

- [18] S. McGettrick, D. Geraghty, and C. McElroy, "Towards an FPGA solver for the PageRank EigenVector Problem," in Parallel Computing: Architectures, Algorithms and Applications, ParCo 2007, Julich and RWTH Aachen, Germany, 2007, pp. 793-800.

- [19] S. McGettrick, D. Geraghty, and C. McElroy, "An FPGA architecture for the Pagerank eigenvector problem," in Field Programmable Logic and Applications, 2008. FPL 2008. International Conference on, 2008, pp. 523-526.

## **Acknowledgements**

It is a pleasure to thank some of the many people who made this work possible. I would like to thank my supervisor, Mr. Dermot Geraghty, for all his support and guidance over the last number of years. Special thanks is also extended to the FIAMMA team, especially Ciarán McElroy who answered all of the many questions I had when I first started working with FPGAs and was always willing to talk through difficulties and discuss possible solutions whenever I needed help. I would like to say thanks to the students and researchers in my lab who always gave support when it was needed.

My family and friends have been most supportive throughout my studies. Particular thanks to my Mam and Dad for giving me the confidence and belief to get this research finished.

Most of all I would like to thank Beth, for all her help.

## **Table of contents**

| 1 |         | ction                                                            |     |

|---|---------|------------------------------------------------------------------|-----|

|   |         | troduction                                                       |     |

|   |         | PGA hardware                                                     |     |

|   | 1.3 Th  | ne FIAMMA Project                                                | 5   |

|   | 1.3.1   |                                                                  | 5   |

|   | 1.4 Co  | ontribution                                                      | 7   |

|   | 1.4.1   | Precision of the PageRank Calculation                            | 7   |

|   | 1.4.2   | PageRank in hardware                                             |     |

|   | 1.4.3   | Implementation and Benchmarking of two generic Linear Algebra    |     |

|   | archite | ctures                                                           | 8   |

|   | 1.4.4   | Implementation and Benchmarking of specialised PageRank hardware | e 9 |

|   |         | ublications                                                      | 9   |

|   | 1.6 Tl  | hesis Guide                                                      | 10  |

| 2 | Techno  | ology Background                                                 | 13  |

|   | 2.1 In  | troduction                                                       | 13  |

|   | 2.2 H   | ardware Design Flow                                              | 14  |

|   | 2.3 Fi  | ield Programmable Gate Arrays (FPGAs)                            | 15  |

|   | 2.3.1   | Development board                                                |     |

|   | 2.3.2   | Virtex-5                                                         |     |

|   | 2.4 M   | Iemory - Double Data Rate SDRAM (SDRAM)                          | 21  |

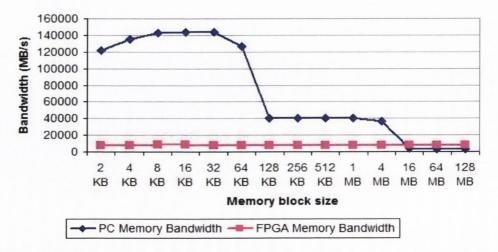

|   | 2.4.1   | PC Memory Hierarchy                                              | 22  |

|   | 2.4.2   | FPGA Memory Hierarchy                                            | 23  |

|   | 2.4.3   | FPGA and PC Memory Hierarchy Compared                            | 25  |

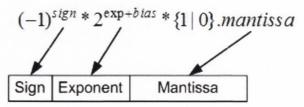

|   | 2.5 N   | lumber representation                                            |     |

|   | 2.5.1   | Floating point                                                   |     |

|   | 2.5.2   |                                                                  |     |

|   |         | ummary                                                           |     |

| 3 |         | et Search                                                        |     |

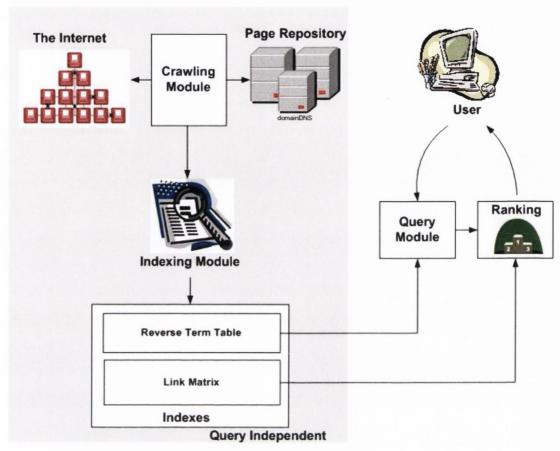

|   |         | ntroduction                                                      |     |

|   | 3.2 C   | Crawling                                                         | 35  |

|   | 3.3 In  | ndexing                                                          | 37  |

|   | 3.4 C   | Ouery Processing                                                 | 39  |

|   | 3.5 R   | Canking                                                          | 40  |

|   | 3.5.1   | Boolean Search Engines                                           | 40  |

|   | 3.5.2   | Latent Semantic Analysis                                         | 41  |

|   | 3.5.3   | Internet Ranking Algorithms                                      | 44  |

|   | 3.5.4   | Hypertext Induced Topic Search (HITS)                            | 45  |

|   | 3.5.5   | PageRank                                                         | 49  |

|   | 3.6 S   | Sparse Matrix by Vector Multiplication                           | 55  |

|   |         |                                                                  |     |

|   | 3.6.1      | Compressed Row/Column Storage                 | 56  |

|---|------------|-----------------------------------------------|-----|

|   | 3.7 Sum    | nmary                                         | 59  |

| 4 | Literature | e Review                                      | 63  |

|   | 4.1 Intro  | oduction                                      | 63  |

|   | 4.2 Inter  | rnet Search                                   | 63  |

|   | 4.2.1      | Alternative PageRank Algorithms               | 64  |

|   | 4.2.2      | Modifications to Power Method for PR          |     |

|   | 4.2.3      | Parallel Computation of PageRank              | 74  |

|   | 4.2.4      | Other FPGA Architectures for Internet Ranking | 75  |

|   | 4.3 SM     | VM                                            | 75  |

|   | 4.3.1      | Optimisation for SMVM in software             | 76  |

|   | 4.3.2      | Specialised hardware for SMVM                 |     |

|   | 4.3.3      | SMVM on FPGAs                                 |     |

|   | 4.4 Arit   | hmetic units on FPGA                          | 89  |

|   | 4.4.1      | Fixed point/Integer arithmetic on FPGA        | 89  |

|   | 4.4.2      | Floating point arithmetic on FPGA             |     |

|   | 4.5 Sum    | nmary                                         |     |

| 5 |            | nd Implementation                             |     |

|   | _          | oduction                                      |     |

|   | 5.2 Arcl   | hitecture                                     | 97  |

|   | 5.2.1      | MicroBlaze                                    |     |

|   | 5.2.2      | Wishbone Bus                                  |     |

|   | 5.2.3      | Wishbone Bus Interface                        | 103 |

|   | 5.2.4      | Wishbone Bus Operations                       |     |

|   | 5.2.5      | PCI Interface                                 |     |

|   | 5.2.6      | Memory Controller                             |     |

|   | 5.3 Vec    | tor Unit                                      | 110 |

|   | 5.4 SM     | VM Architecture 1 - SPAR                      | 114 |

|   | 5.4.1      | SPAR Modifications                            | 118 |

|   | 5.5 SM     | VM Architecture 2 - SCAR                      | 119 |

|   | 5.5.1      | SCAR Data Structure                           | 122 |

|   | 5.5.2      | SCAR Hardware                                 | 125 |

|   | 5.5.3      | Dual SCAR architecture                        | 127 |

|   | 5.6 SM     | VM Architecture 3 – PageRank SMVM             |     |

|   | 5.6.1      | Removing SMVM from PageRank                   | 130 |

|   | 5.6.2      | PageRank Hardware                             |     |

|   | 5.6.3      | Dual path solution                            |     |

|   | 5.7 Bus    | Contention on SMVM architectures              |     |

|   | 5.8 Soft   | ware                                          | 139 |

|   | 5.8.1      | Software on Host PC                           | 139 |

|   | 5.8.2      | Hardware Communication kernels                | 139 |

|   | 5.8.3      | Programming the MicroBlaze                    |     |

|   |            | imary                                         |     |

| 6 |            |                                               |     |

|   |            | oduction                                      |     |

|   |            | chmark Matrices                               |     |

|   |            | eral Purpose Processor results                |     |

|   |            | ting Point PageRank Performance on Virtex-II  |     |

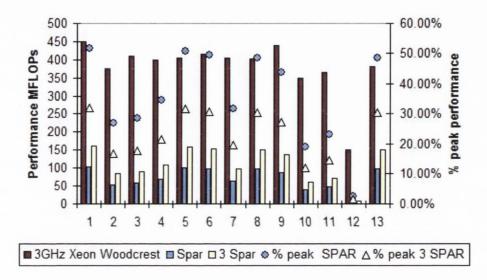

|   | 6.4.1      | SMVM Architecture 1 – SPAR                    | 150 |

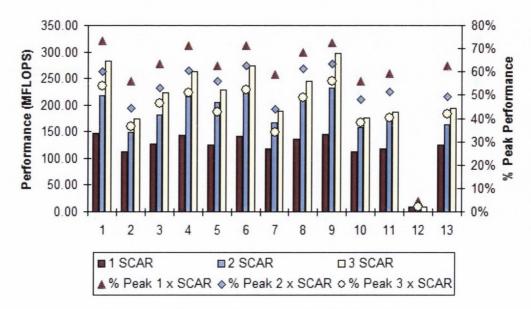

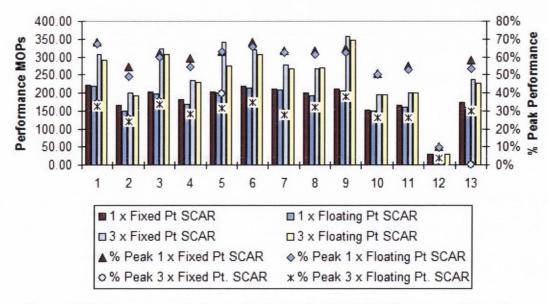

|   |            | SMVM Architecture 2 – SCAR                    |     |

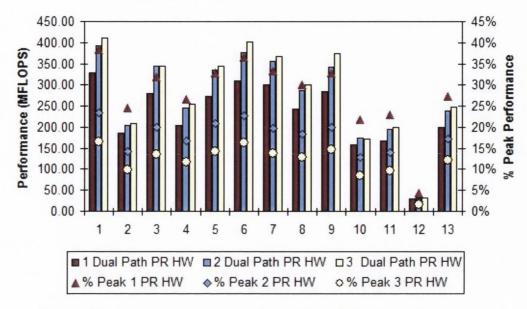

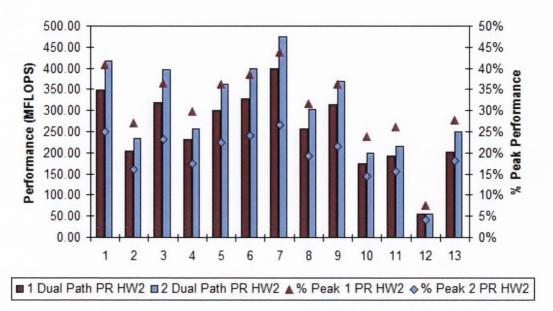

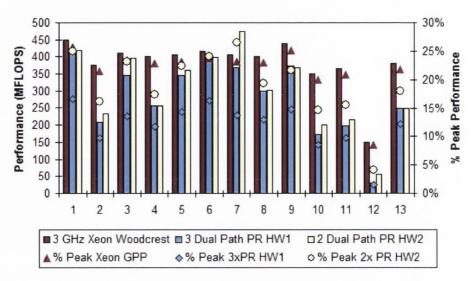

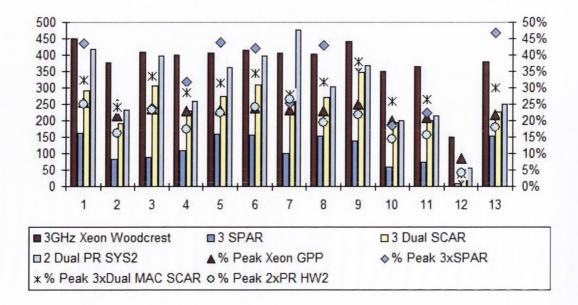

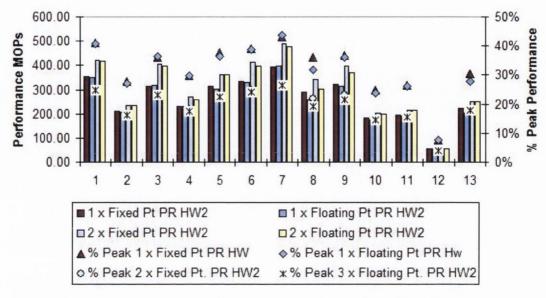

|    | 6.4.3      | SMVM Architecture 3 – PageRank HW                           | 157   |

|----|------------|-------------------------------------------------------------|-------|

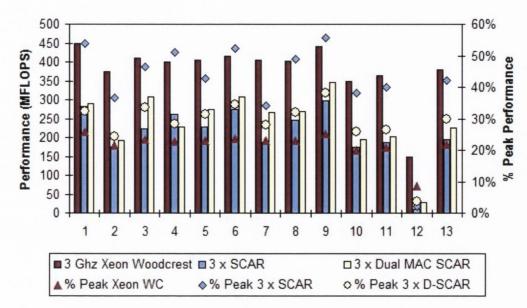

|    | 6.4.4      | SMVM Architectures Compared                                 |       |

|    | 6.5 Perf   | ormance Limitations                                         |       |

|    | 6.5.1      | Bus Contention                                              | 165   |

|    | 6.5.2      | Load Balancing                                              | 170   |

|    | 6.5.3      | Measuring NOP frequency                                     |       |

|    | 6.6 Prec   | ision                                                       | 176   |

|    | 6.6.1      | Fixed point Emulation                                       | 176   |

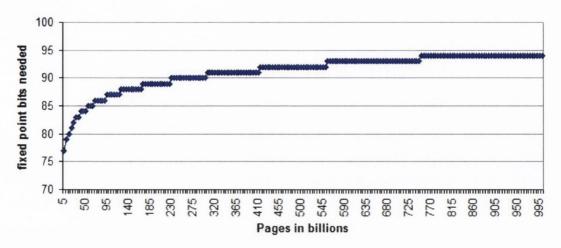

|    | 6.6.2      | Zipfian distributions                                       | 179   |

|    | 6.7 Fixe   | ed Point Performance on Virtex-II                           | 181   |

|    | 6.7.1      | Fixed Point SCAR implementation                             | 182   |

|    | 6.7.2      | Fixed Point PageRank HW implementation                      | 184   |

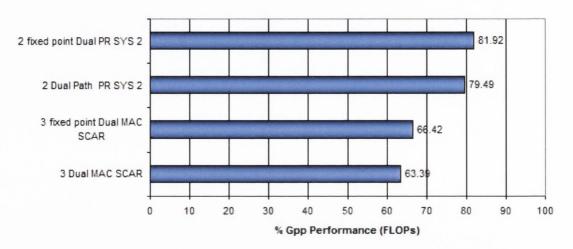

|    | 6.7.3      | Fixed Point Architecture compared                           | 185   |

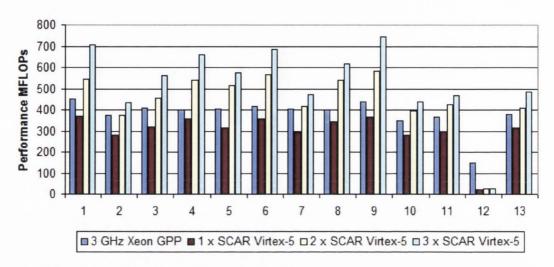

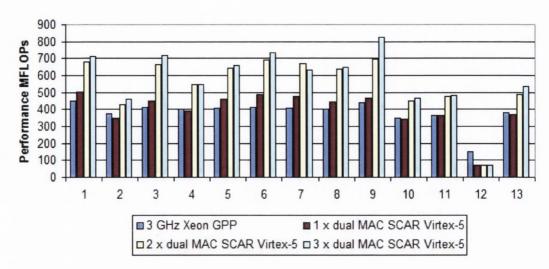

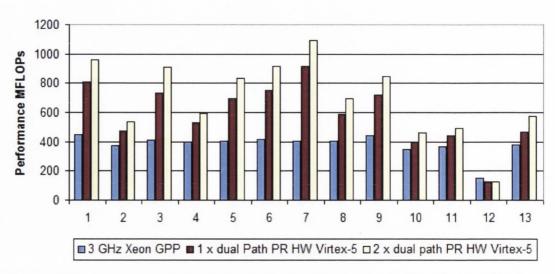

|    | 6.8 Floa   | ting Point Performance on Virtex-5                          | 186   |

|    | 6.9 Sum    | nmary                                                       | 191   |

| 7  | Discussion | on and Conclusions                                          | 197   |

|    | 7.1 Intro  | oduction                                                    | 197   |

|    | 7.2 Con    | tribution of this Thesis                                    | 198   |

|    | 7.2.1      | Precision of the PageRank calculation                       | 198   |

|    | 7.2.2      | PageRank in Hardware                                        |       |

|    | 7.2.3      | Implementation and Benchmarking of two Generic Linear Algeb | ra    |

|    | Systems    | 200                                                         |       |

|    | 7.2.4      | Implementation and Benchmarking of specialised PageRank Har | dware |

|    |            | 202                                                         |       |

|    |            | itations and Future Work                                    |       |

|    |            | l Thoughts                                                  |       |

| 8  |            | es                                                          |       |

| 9  | 11         | x 1: FE Matrices                                            |       |

| 1( | ) Appen    | dix 2: Source Code                                          | 223   |

## **List of figures**

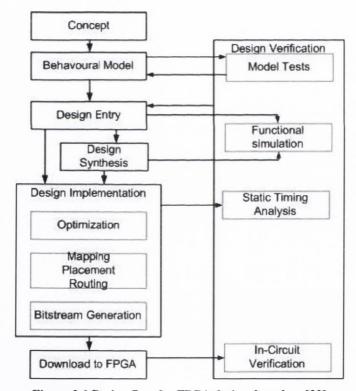

| Figure 2.1 Design flow for FPGA design, based on [22]                              | 14  |

|------------------------------------------------------------------------------------|-----|

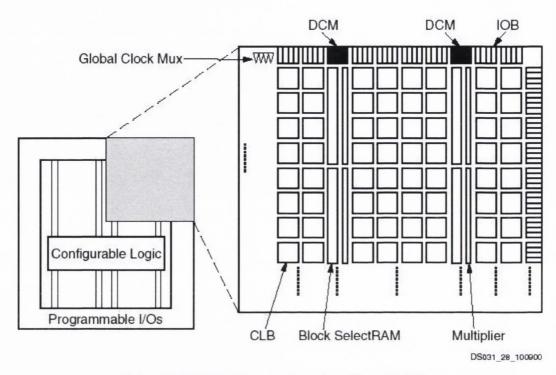

| Figure 2.2 FPGA Architecture Overview (Virtex-II) [15]                             | 16  |

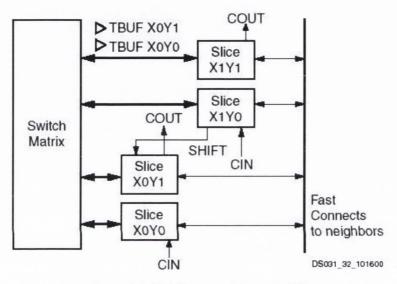

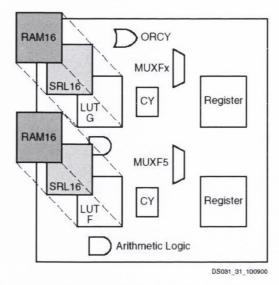

| Figure 2.3 CLB Element (Virtex-II) [15]                                            |     |

| Figure 2.4 Slice Configuration (Virtex-II) [15]                                    | 18  |

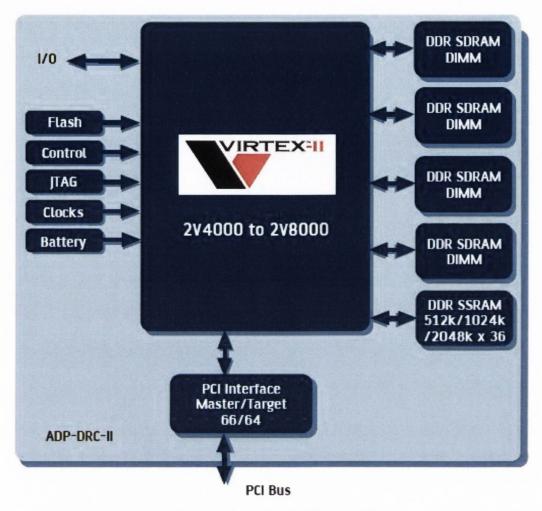

| Figure 2.5 Alpha-Data ADP-DRCII board [28]                                         |     |

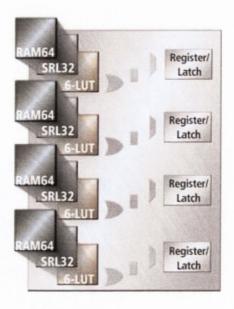

| Figure 2.6 Virtex-5 Logic Block                                                    |     |

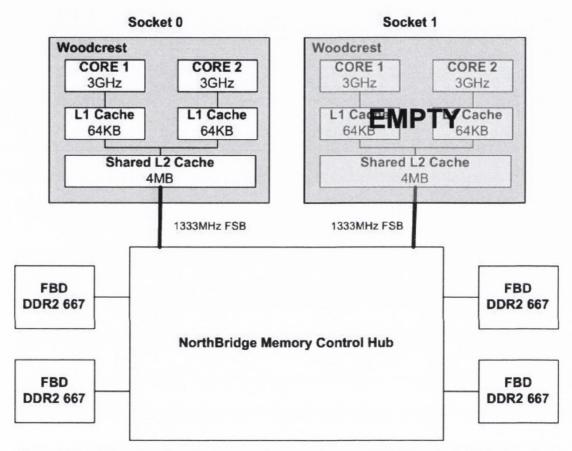

| Figure 2.7 Intel Xeon Woodcrest memory architecture, based on [38] (L1 cache is    |     |

| 32KB data & 32KB Instruction)                                                      | 23  |

| Figure 2.8 Memory Bandwidth of the Xeon Woodcrest and FPGA for various mem         | ory |

| block sizes.                                                                       | 26  |

| Figure 2.9 Floating point number                                                   | 28  |

| Figure 3.1 Overview of a Search Engine                                             | 35  |

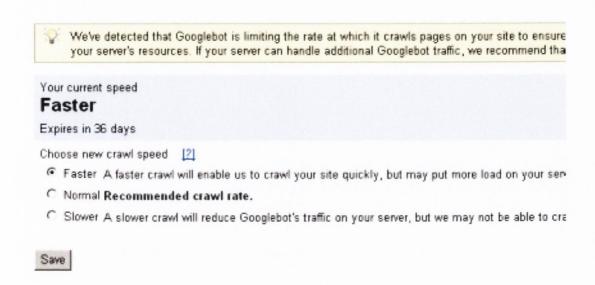

| Figure 3.2 Google Webmaster controls                                               |     |

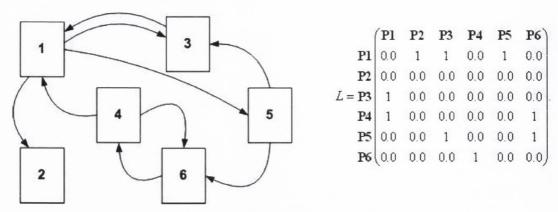

| Figure 3.3 Link matrix created from crawled pages                                  |     |

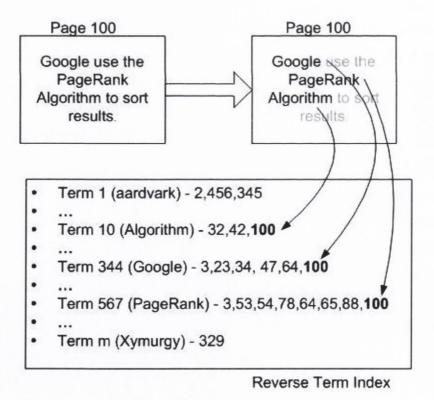

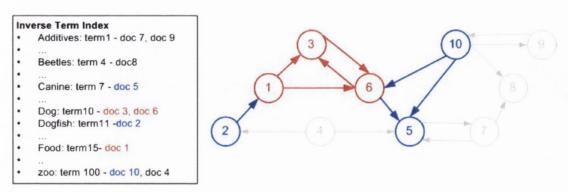

| Figure 3.4 Reverse Term Index creation                                             |     |

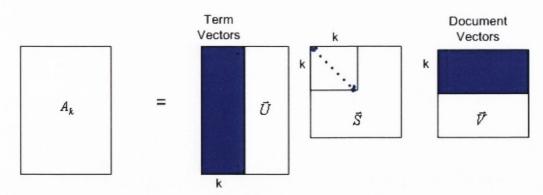

| Figure 3.5 The truncation of the S,U and V matrices in LSA                         | 43  |

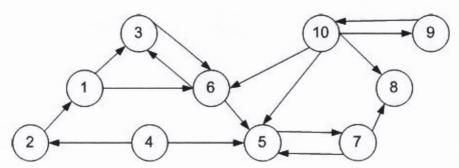

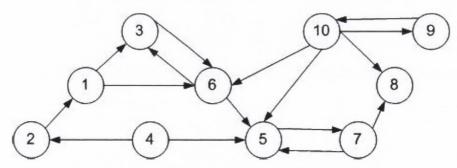

| Figure 3.6 Example of a 10 Node Neighbourhood graph                                |     |

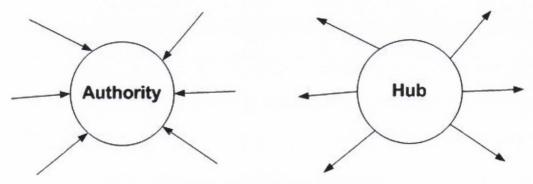

| Figure 3.7 An Authority node and a Hub node                                        | 45  |

| Figure 3.8 Building a neighbourhood graph in HITS                                  | 47  |

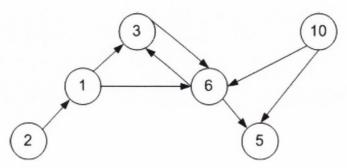

| Figure 3.9 Finalised neighbourhood graph for "dog food" query                      | 47  |

| Figure 3.10 Link matrix for HITS neighbourhood graph                               | 48  |

| Figure 3.11 Matlab code for HITS ranking Algorithm                                 | 48  |

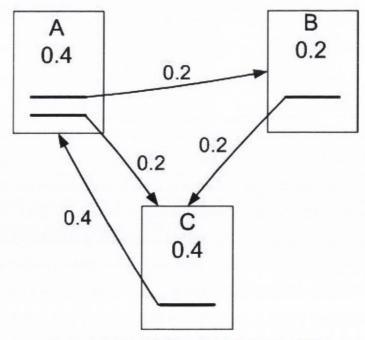

| Figure 3.12 Simplified PageRank Calculation [49]                                   |     |

| Figure 3.13 Sample Web for PageRank adjacency matrix                               | 51  |

| Figure 3.14 PageRank adjacency Matrix                                              |     |

| Figure 3.15 Matlab code for PageRank ranking Algorithm                             | 54  |

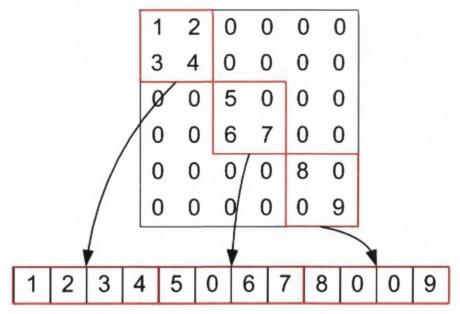

| Figure 3.16 Sparse Matrix by Vector Multiplication                                 |     |

| Figure 3.17 CRS vectors of A matrix in Figure 3.16                                 | 57  |

| Figure 3.18 CCS vectors of A matrix in Figure 3.16                                 | 57  |

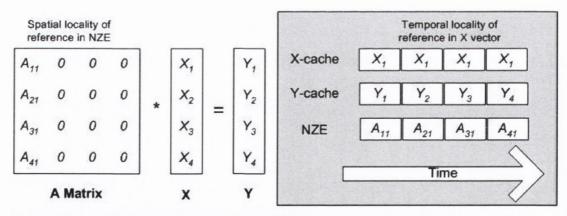

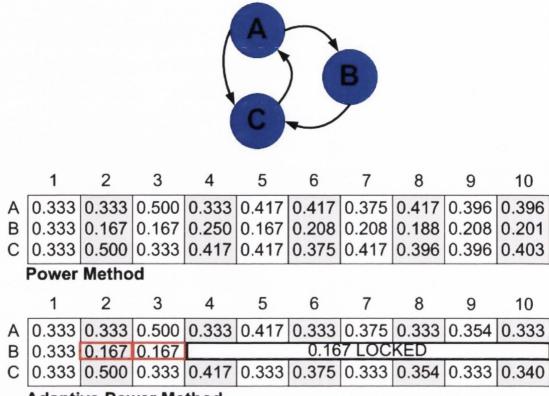

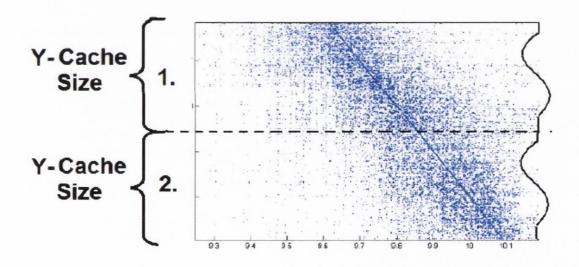

| Figure 3.19 Spatial locality of reference in the NZE leads to temporal locality of |     |

| reference in X and Y vectors.                                                      | 58  |

| Figure 3.20 Matrix with poor spatial locality increase the number of cache misses  |     |

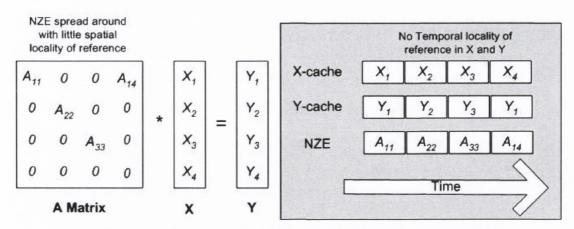

| Figure 4.1 Adaptive power method mis-identified convergence                        | 68  |

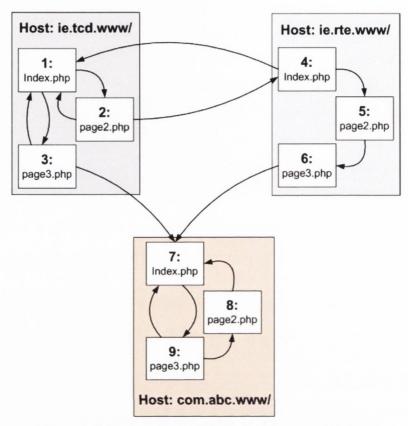

| Figure 4.2 Example of Internet divided into hosts for Blockrank                    |     |

| Figure 4.3 Adjacency matrix for Internet shown in Figure 4.2                       | 70  |

| Figure 4.4 Local and Global adjacency matrices for Internet shown in Figure 4.2    | 71  |

| Figure 4.5 Register blocking dense block scheme to increase data reuse             |     |

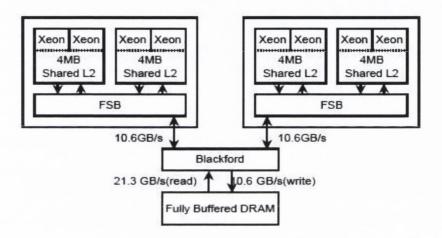

| Figure 4.6 Clovertown memory hierarchy [37, 86]                                    | 79  |

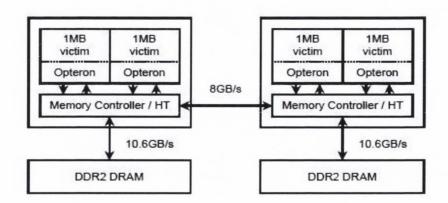

| Figure 4.7 AMD Opteron memory hierarchy [86]                                       | 79  |

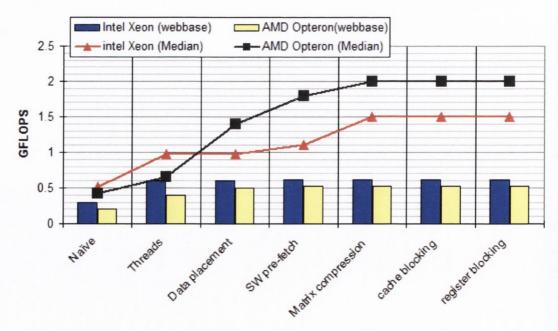

| Figure 4.8 Webbase matrix performance on Intel Xeon and AMD Opteron [37] (Ba                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rs on                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| the graph represent the performance of the IA matrix on the Xeon and AMD process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | sor                                                                                                                                                                                          |

| respectively. The line graphs represent the median performance of Williams test set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                              |

| showing a large discrepancy between IA matrices and other Sparse matrices.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 80                                                                                                                                                                                           |

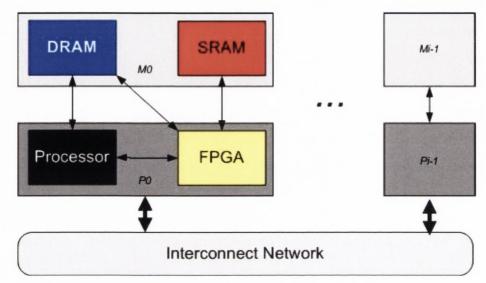

| Figure 4.9 Zhuo and Prasanna's system model [13]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86                                                                                                                                                                                           |

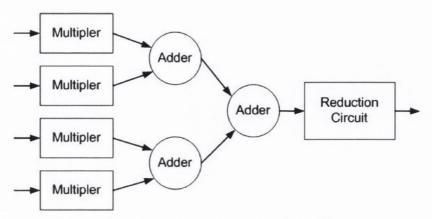

| Figure 4.10 SMVM architecture used by Zhuo and Prasanna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 87                                                                                                                                                                                           |

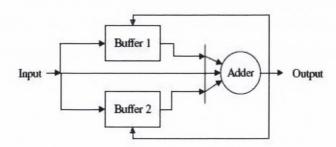

| Figure 4.11 Reduction circuit used by Zhuo and Prasanna [96]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 87                                                                                                                                                                                           |

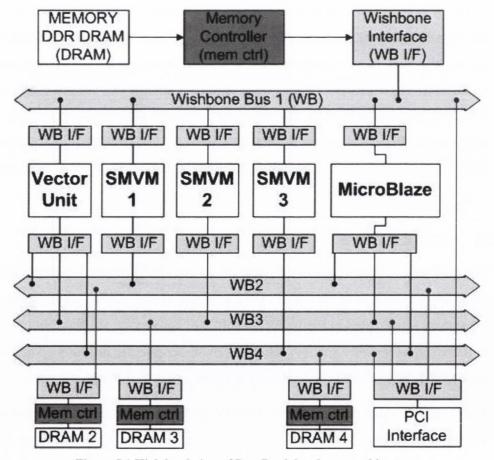

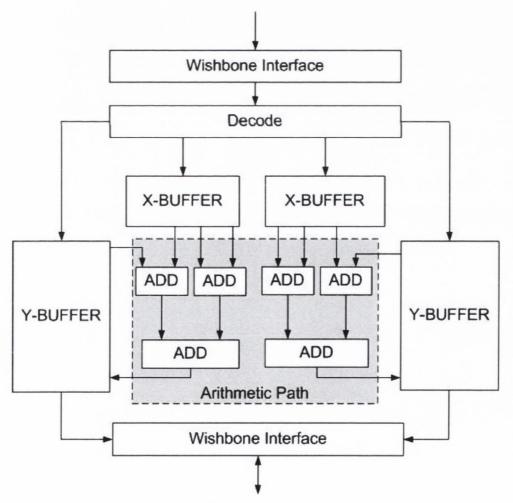

| Figure 5.1 High level view of PageRank hardware architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 00                                                                                                                                                                                           |

| Figure 5.1 High level view of FageKank natuwate architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 90                                                                                                                                                                                           |

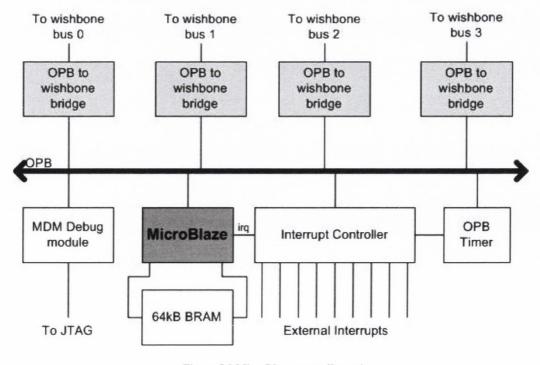

| Figure 5.2 MicroBlaze controller unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 102                                                                                                                                                                                          |

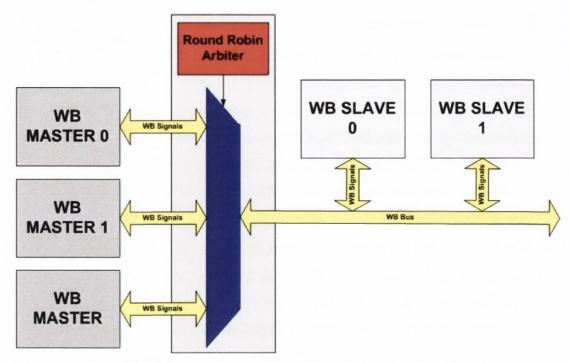

| Figure 5.3 Wishbone multiplexed Shared bus with round robin arbiter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 104                                                                                                                                                                                          |

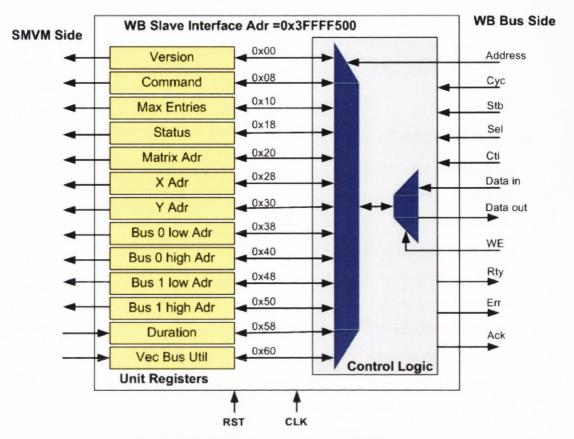

| Figure 5.4 Wishbone slave interface for SMVM unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 104                                                                                                                                                                                        |

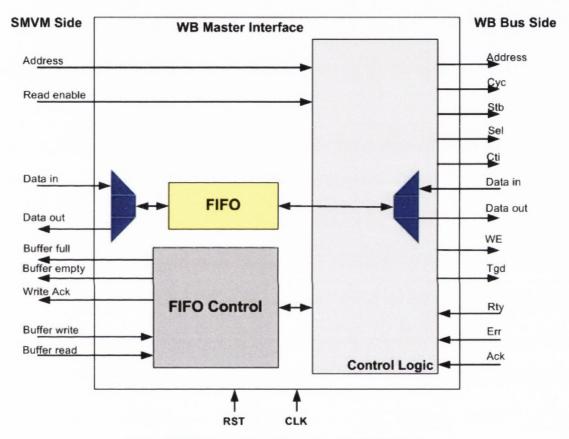

| Figure 5.5 Wishbone Master Interface for SMVM unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                              |

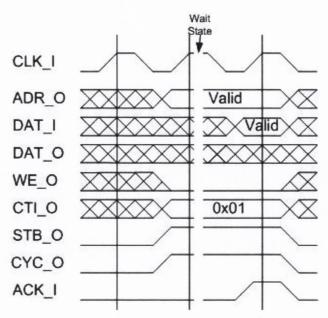

| Figure 5.6 Wishbone single read timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                              |

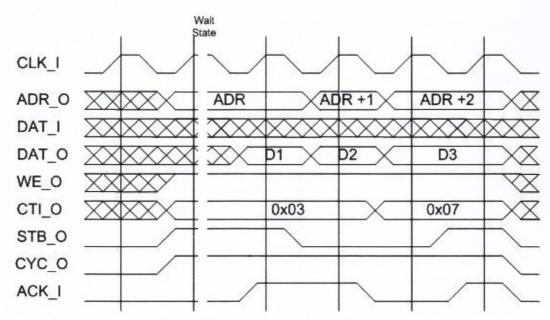

| Figure 5.7 Wishbone block write timing diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                              |

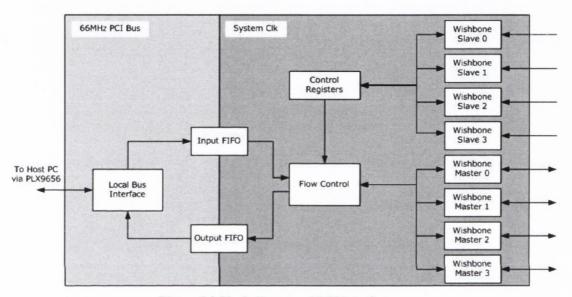

| Figure 5.8 Block diagram of PCI interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                              |

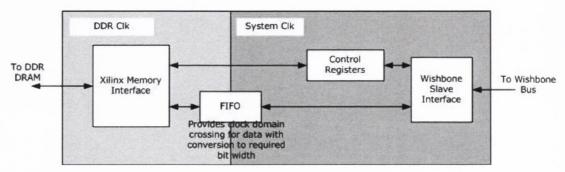

| Figure 5.9 Overview of memory controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                              |

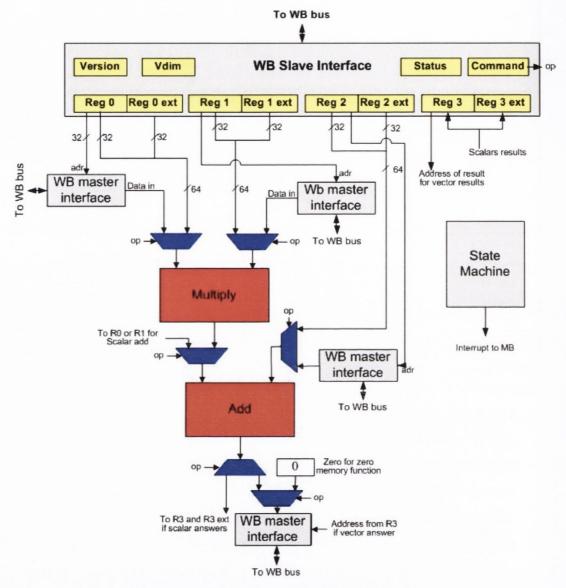

| Figure 5.10 Block diagram of Hardware Vector unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 112                                                                                                                                                                                        |

| Figure 5.11 Vector unit command word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 113                                                                                                                                                                                        |

| Figure 5.12 SPAR storage format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .115                                                                                                                                                                                         |

| Figure 5.13 SPAR architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .116                                                                                                                                                                                         |

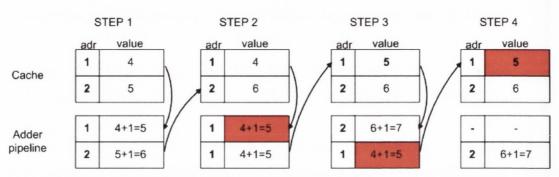

| Figure 5.14 Example of a RAW hazard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .118                                                                                                                                                                                         |

| Figure 5.15 SPAR strip reordering scheme to eliminate Y-cache misses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 119                                                                                                                                                                                        |

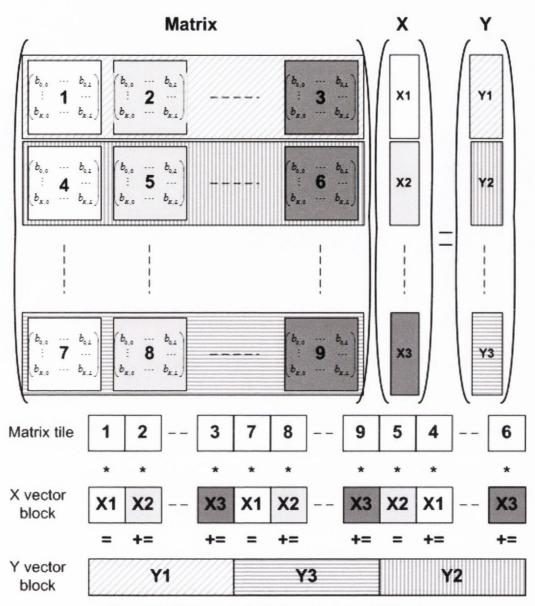

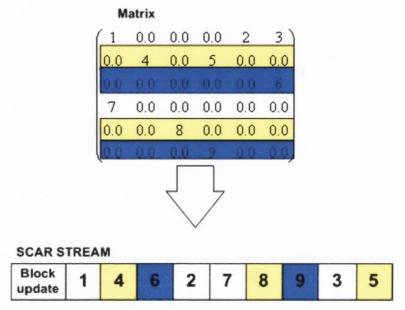

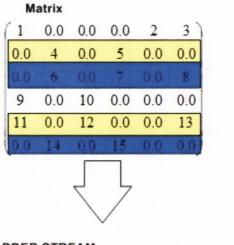

| Figure 5.16 NxM matrix divided into blocks for SCAR unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                              |

| Figure 5.17 SCAR data words A) block update B) matrix data point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

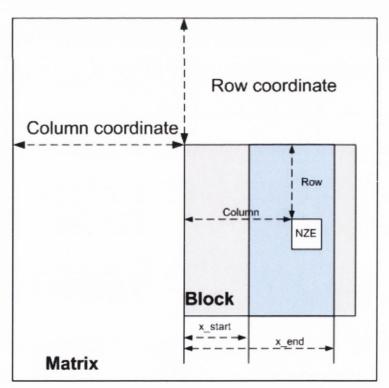

| Figure 5.18 absolute and relative addressing as used in the SCAR data format. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                              |

| column and row coordinates contained in the block update contain the absolute add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ress                                                                                                                                                                                         |

| column and row coordinates contained in the block update contain the absolute addresses are given relative to the block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                              |

| of the matrix in the matrix and all other addresses are given relative to the block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                              |

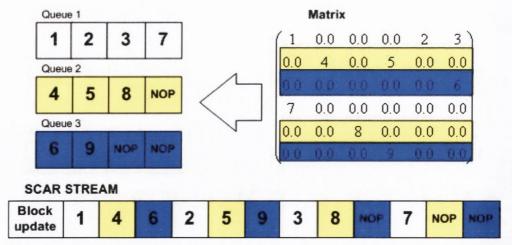

| of the matrix in the matrix and all other addresses are given relative to the block Figure 5.19 Simple SCAR reordering (using round robin system between the three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 123                                                                                                                                                                                        |

| of the matrix in the matrix and all other addresses are given relative to the block Figure 5.19 Simple SCAR reordering (using round robin system between the three queues)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 123                                                                                                                                                                                        |

| of the matrix in the matrix and all other addresses are given relative to the block Figure 5.19 Simple SCAR reordering (using round robin system between the three queues) Figure 5.20 Opportunistic reordering in SCAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 123<br>. 124<br>. 125                                                                                                                                                                      |

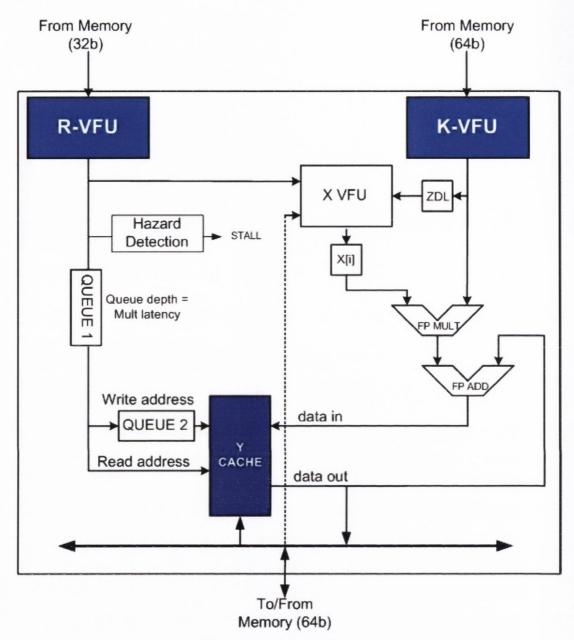

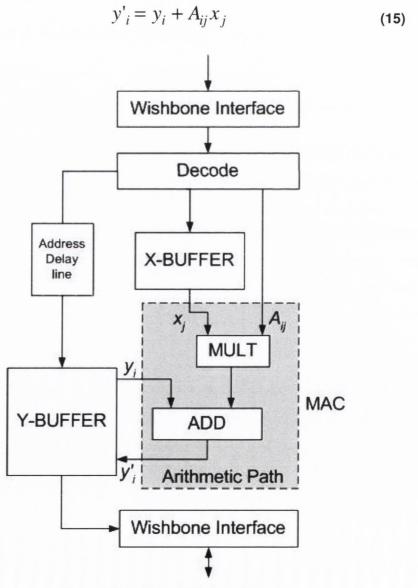

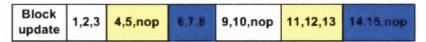

| of the matrix in the matrix and all other addresses are given relative to the block Figure 5.19 Simple SCAR reordering (using round robin system between the three queues) Figure 5.20 Opportunistic reordering in SCAR. Figure 5.21 Outline of SCAR architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 123<br>. 124<br>. 125<br>. 126                                                                                                                                                             |

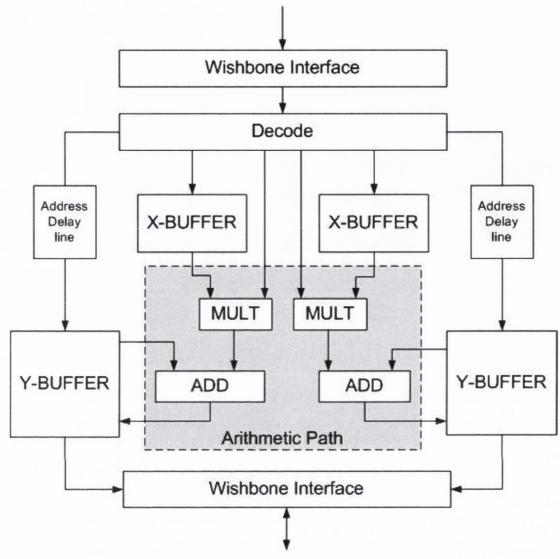

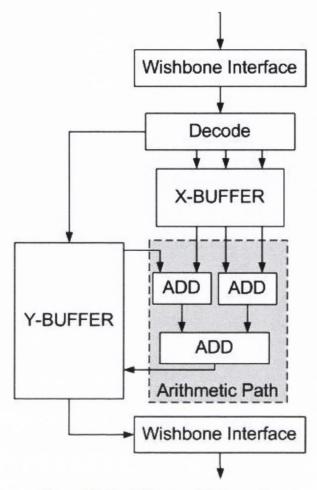

| of the matrix in the matrix and all other addresses are given relative to the block Figure 5.19 Simple SCAR reordering (using round robin system between the three queues) Figure 5.20 Opportunistic reordering in SCAR Figure 5.21 Outline of SCAR architecture Figure 5.22 Block diagram of Dual SCAR architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 123<br>. 124<br>. 125<br>. 126<br>. 129                                                                                                                                                    |

| of the matrix in the matrix and all other addresses are given relative to the block Figure 5.19 Simple SCAR reordering (using round robin system between the three queues) Figure 5.20 Opportunistic reordering in SCAR Figure 5.21 Outline of SCAR architecture Figure 5.22 Block diagram of Dual SCAR architecture Figure 5.23 Example of PageRank SMVM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 123<br>. 124<br>. 125<br>. 126<br>. 129<br>. 130                                                                                                                                           |

| of the matrix in the matrix and all other addresses are given relative to the block Figure 5.19 Simple SCAR reordering (using round robin system between the three queues) Figure 5.20 Opportunistic reordering in SCAR Figure 5.21 Outline of SCAR architecture Figure 5.22 Block diagram of Dual SCAR architecture Figure 5.23 Example of PageRank SMVM Figure 5.24 The new column value vector and pattern matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 123<br>. 124<br>. 125<br>. 126<br>. 129<br>. 130                                                                                                                                           |

| of the matrix in the matrix and all other addresses are given relative to the block Figure 5.19 Simple SCAR reordering (using round robin system between the three queues) Figure 5.20 Opportunistic reordering in SCAR Figure 5.21 Outline of SCAR architecture Figure 5.22 Block diagram of Dual SCAR architecture Figure 5.23 Example of PageRank SMVM Figure 5.24 The new column value vector and pattern matrix Figure 5.25 Replacing SMVM in PageRank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 123<br>. 124<br>. 125<br>. 126<br>. 129<br>. 130<br>. 131                                                                                                                                  |

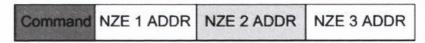

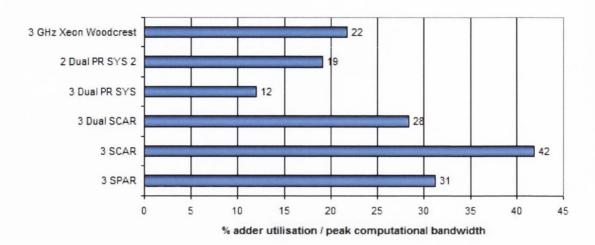

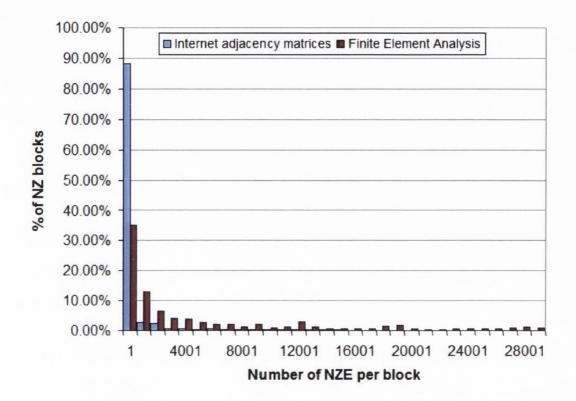

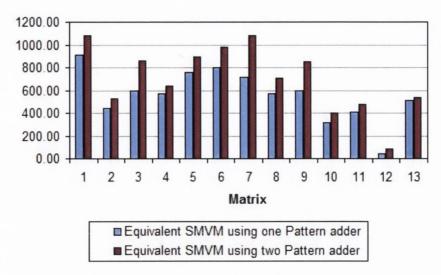

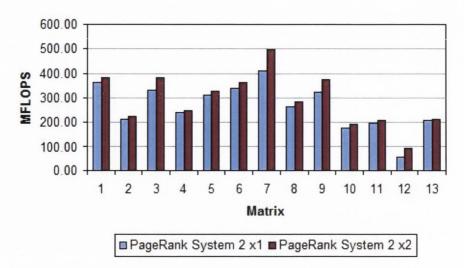

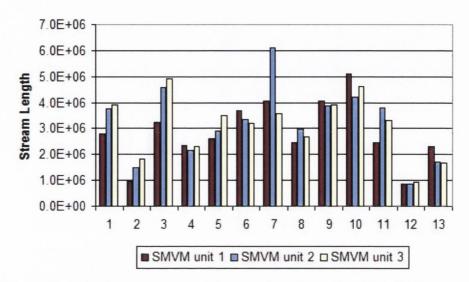

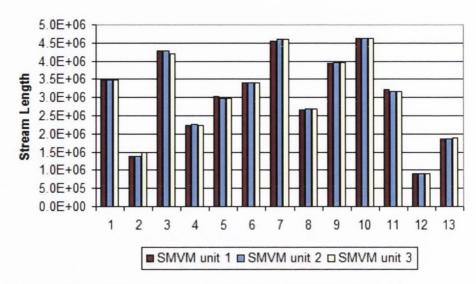

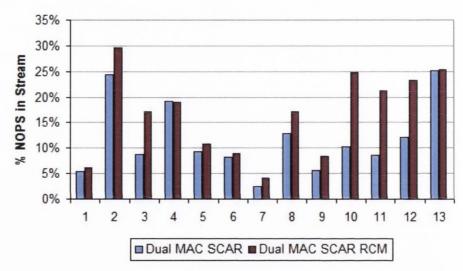

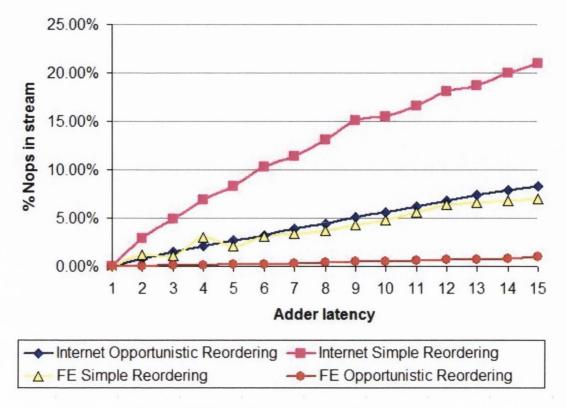

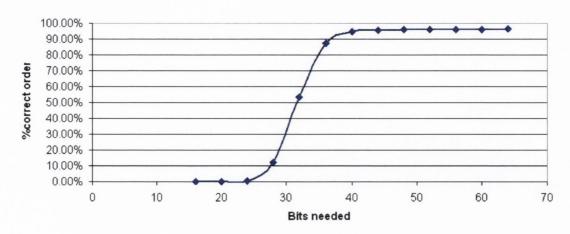

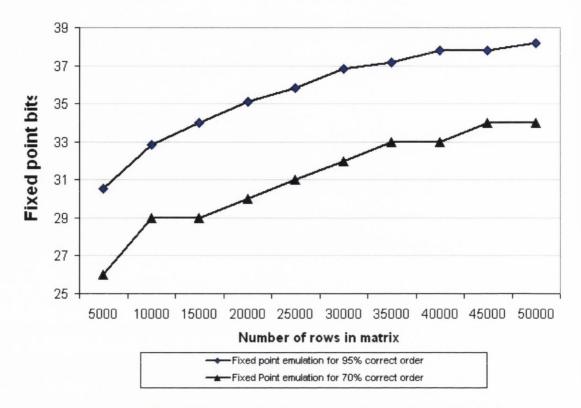

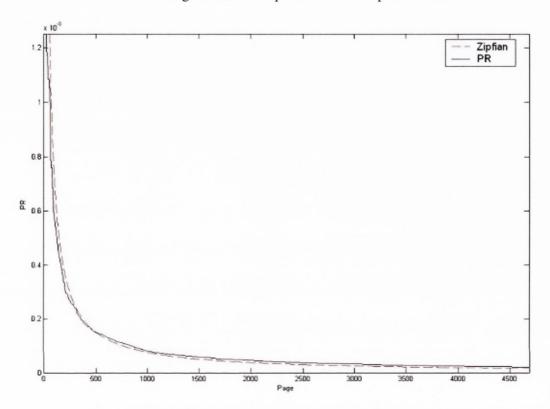

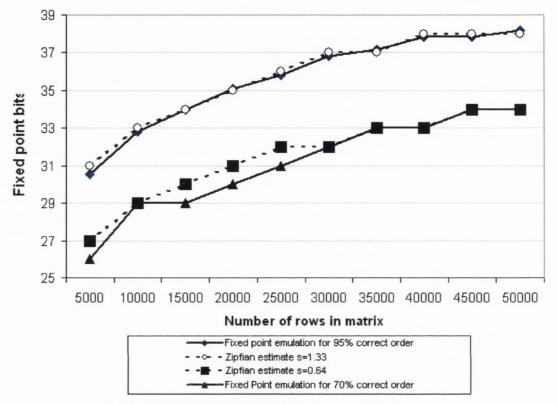

| of the matrix in the matrix and all other addresses are given relative to the block Figure 5.19 Simple SCAR reordering (using round robin system between the three queues) Figure 5.20 Opportunistic reordering in SCAR Figure 5.21 Outline of SCAR architecture Figure 5.22 Block diagram of Dual SCAR architecture Figure 5.23 Example of PageRank SMVM Figure 5.24 The new column value vector and pattern matrix Figure 5.25 Replacing SMVM in PageRank Figure 5.26 Pattern adder data word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 123<br>. 124<br>. 125<br>. 126<br>. 129<br>. 130<br>. 131<br>. 132                                                                                                                         |