Program Generation for Intel AES New Instructions Thesis submitted for the degree of Doctor in Philosophy

2011

Raymond Keith Scott Manley

## Declaration

I declare that this thesis has not been submitted as an exercise for a degree at this or any other university and it is entirely my own work.

I agree to deposit this thesis in the University's open access institutional repository or allow the Library to do so on my behalf, subject to Irish Copyright Legislation and Trinity College Library conditions of use and acknowledgement.

Raymond Keith Scott Manley

## Acknowledgements

The work presented in this dissertation could have not been completed without the knowledge, experience, and support of my supervisor, Dr. David Gregg. He ensured several years ago that I got the opportunity to study in Ireland. I am as equally thankful to him for that as I am for his influence on my academic pursuits.

I would also like to thank Jason McCandless, Kevin Williams, Paul Biggar, Nicholas Nash, and Bobb Crosbie. As far as research groups go, the members of our group were a social and enjoyable bunch to talk to, both inside and outside the office.

I could not have done any of this work without funding. I would like to thank IRCSET (The Irish Research Council for Science, Engineering and Technology) and Intel Ireland for providing me this unique opportunity.

I would like to thank all my friends on both sides of the pond and specifically to my proofreaders: Aoife Carolan, Marianne Cassidy, and Sophie Geary. Finally, I would like to thank my parents. I know they would have liked to see me more over this period, but they have been incredibly understanding and supporting of my endeavours throughout the years. This work is dedicated to them.

## Abstract

High-performance primitive libraries are used to replace parts of sub-optimal code with optimized implementations. These libraries often come in the form of highly-optimized assembly routines, which raises several issues. Small changes to assembly routines can require significant rewrites. New versions of microarchitectures will often require changes in the assembly to keep code both efficient and functional. Maintaining multiple versions of the same basic piece of assembly code is a costly software engineering problem. One approach to solving this problem is using a program generator.

AES-NI is an instruction-set extension on Intel processors that implement a full round of AES encryption in a single instruction. Existing libraries use hand-tuned assembly language to overlap the execution of multiple AES instructions to extract maximum performance. In this dissertation, we argue that using a program generator is suitable substitute for writing highly-optimized assembly routines that use AES-NI. We present a program generation system that seamlessly integrates high-level algorithmic choices with scheduling strategies that exploit instruction-level parallelism.

This program generation system returns AES implementations that achieve near optimal performance. We also show that the generator is dynamic enough to take exploratory approaches when optimizing code. As a result, this dissertation also contributes two novel encryption modifications. For CTR mode, we present a "mixedmode" operation that combines traditional lookup table optimizations with AES-NI instructions. In cyclic modes, such as CBC, we show how manipulating the **xor** instructions can shorten the chain of dependent operations. These optimized implementations are found using an adapted simulated annealing algorithm. We show these implementations can achieve similar or superior cycle per byte times compared to the high-performance library versions provided by Intel. The end result is a program generation technique that could potentially be adapted to optimize other algorithms that rely on instruction-set extensions.

## Contents

| A  | bstra  | $\mathbf{ct}$ |                                 | v    |

|----|--------|---------------|---------------------------------|------|

| Li | ist of | Table         | S                               | xi   |

| Li | ist of | Figur         | es                              | xiii |

| Li | ist of | Code          | Listings                        | xv   |

| 1  | Mo     | tivatio       | n                               | 1    |

|    | 1.1    | Thesis        | 3                               | 3    |

|    | 1.2    | Contri        | ibutions                        | 3    |

|    | 1.3    | Releva        | ant Academic Publications       | 5    |

|    | 1.4    | Disser        | tation Outline                  | 5    |

| 2  | Bac    | kgrou         | nd                              | 7    |

|    | 2.1    | Archit        | tectural Features               | 7    |

|    |        | 2.1.1         | Instruction Pipelining          | 7    |

|    |        | 2.1.2         | Superscalar                     | 9    |

|    |        | 2.1.3         | Simultaneous Multithreading     | 10   |

|    |        | 2.1.4         | Vector/SIMD                     | 11   |

|    |        | 2.1.5         | Autovectorization               | 12   |

|    | 2.2    | Softwa        | are ILP Optimizations           | 13   |

|    |        | 2.2.1         | Instruction Scheduling          | 13   |

|    |        | 2.2.2         | Loop Unrolling                  | 13   |

|    |        | 2.2.3         | Software Pipelining             | 14   |

|    |        | 2.2.4         | Modulo Scheduling               | 15   |

|    | 2.3    | Progra        | am Generation                   | 17   |

|    |        | 2.3.1         | Domain Specific Code Generators | 18   |

|    |        | 2.3.2         | Traversing the Search Space     | 19   |

### CONTENTS

|          |               | 2.3.3 Simulated Annealing                    |

|----------|---------------|----------------------------------------------|

|          | 2.4           | Streaming Languages                          |

| 3        | Vec           | tor Code Generation for GPPs 27              |

|          | 3.1           | Introduction                                 |

|          | 3.2           | Brook                                        |

|          | 3.3           | Modifications to Brook                       |

|          |               | 3.3.1 Modifying the Code Generator           |

|          |               | 3.3.2 Modifying the Runtime                  |

|          | 3.4           | Generating Vector Code                       |

|          |               | 3.4.1 General operations                     |

|          |               | 3.4.2 Arrays                                 |

|          |               | 3.4.3 Conditional Assignments                |

|          |               | 3.4.4 For loops inside kernels               |

|          |               | 3.4.5 Reduce Kernels                         |

|          |               | 3.4.6 Selective Vectorization                |

|          | 3.5           | Results                                      |

|          |               | 3.5.1 Analyzing Performance                  |

|          | 3.6           | Related Work                                 |

|          | 3.7           | Conclusion                                   |

| 4        | AE            | S Encryption in Software and Hardware 47     |

|          | 4.1           | AES                                          |

|          | 4.2           | Block Cipher Modes                           |

|          |               | 4.2.1 Parallel Modes                         |

|          |               | 4.2.2 Cyclic Modes                           |

|          |               | 4.2.3 Combined Encryption and Authentication |

|          | 4.3           | AES Software Acceleration                    |

|          | 4.4           | AES Hardware Acceleration                    |

|          | 4.5           | Intel AES-NI                                 |

|          | 4.6           | Conclusion                                   |

| <b>5</b> | $\mathbf{CT}$ | R and CBC Program Generation 67              |

|          | 5.1           | Introduction                                 |

|          | 5.2           | CTR and CBC Code Generation                  |

|          |               | 5.2.1 CTR Optimizations                      |

|          |               | 5.2.2 Optimizations for Both Modes           |

### CONTENTS

|   |     | 5.2.3   | CBC Optimizations                                                                                     | 73  |

|---|-----|---------|-------------------------------------------------------------------------------------------------------|-----|

|   |     | 5.2.4   | Simulated Annealing                                                                                   | 75  |

|   | 5.3 | Result  | s                                                                                                     | 76  |

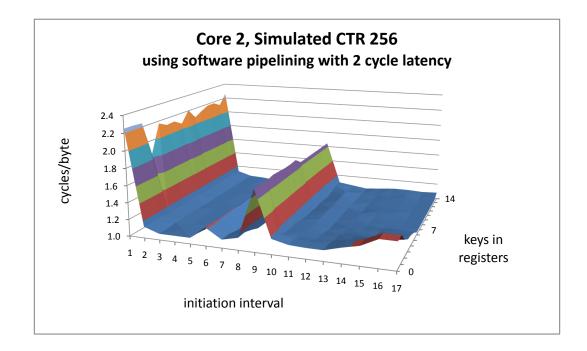

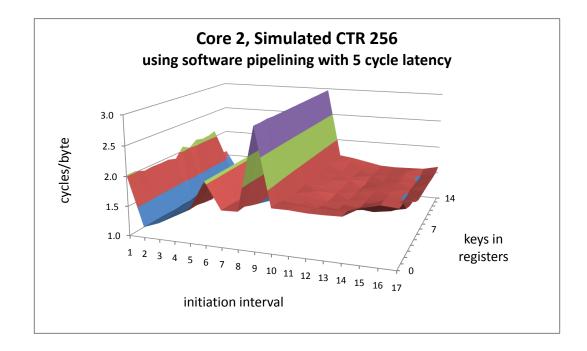

|   |     | 5.3.1   | Cycles per Byte                                                                                       | 78  |

|   |     | 5.3.2   | Selective-Exhaustive Searches                                                                         | 78  |

|   |     | 5.3.3   | Guided Search using Simulated Annealing $\ldots \ldots \ldots \ldots \ldots$                          | 86  |

|   | 5.4 | Conclu  | asion                                                                                                 | 89  |

| 6 | Gen | eralize | ed AES Program Generation                                                                             | 91  |

|   | 6.1 | Introd  | uction                                                                                                | 91  |

|   | 6.2 | GEN1    | vs. AES-GEN                                                                                           | 93  |

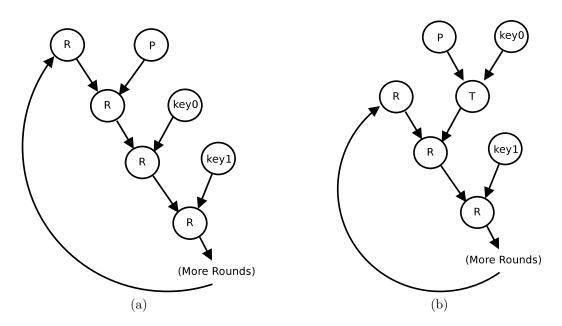

|   |     | 6.2.1   | Function Stitching                                                                                    | 94  |

|   |     | 6.2.2   | Cycles per Round                                                                                      | 94  |

|   | 6.3 | The A   | ES-GEN Program Generator                                                                              | 95  |

|   |     | 6.3.1   | Algorithmic Choices with Cheetah                                                                      | 96  |

|   |     | 6.3.2   | The ILP Optimizer                                                                                     | 98  |

|   |     | 6.3.3   | Code Tuning $\ldots$ | 101 |

|   | 6.4 | Genera  | ator Flexibility with Parallel Algorithms                                                             | 102 |

|   |     | 6.4.1   | Counter (CTR) $\ldots$                                                                                | 102 |

|   |     | 6.4.2   | Electronic Codebook (ECB)                                                                             | 107 |

|   |     | 6.4.3   | Performance Observations for CTR and ECB Modes $\ \ . \ . \ .$ .                                      | 109 |

|   | 6.5 | Algori  | thmic Variations with Cyclic Algorithms                                                               | 110 |

|   |     | 6.5.1   | Cipher-Block Chaining (CBC)                                                                           | 110 |

|   |     | 6.5.2   | PCBC, CFB, and OFB                                                                                    | 113 |

|   |     | 6.5.3   | Applicability of XOR Optimizations to Other AES Modes $\ . \ .$ .                                     | 115 |

|   | 6.6 | Combi   | ning Algorithms via Function Stitching                                                                | 116 |

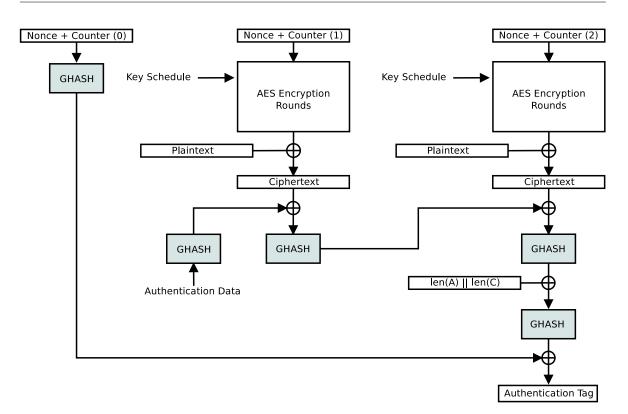

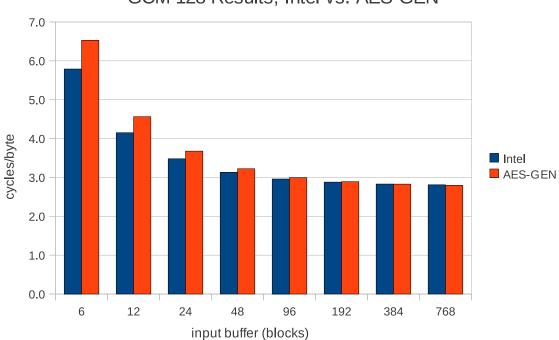

|   |     | 6.6.1   | Galois/Counter Mode (GCM) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                   | 116 |

|   |     | 6.6.2   | Counter with CBC-MAC (CCM) $\ldots \ldots \ldots \ldots \ldots \ldots$                                | 118 |

|   | 6.7 | Experi  | imental Results                                                                                       | 119 |

|   |     | 6.7.1   | Generated Code Performance $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                  | 120 |

|   |     | 6.7.2   | AES-GEN vs Hand-tuned Assembly                                                                        | 124 |

|   |     | 6.7.3   | Why Not Optimize with a Standard Compiler? $\ldots$                                                   | 128 |

|   | 6.8 | Relate  | d Work                                                                                                | 131 |

|   | 6.9 | Conclu  | nsion                                                                                                 | 132 |

#### CONTENTS

| <b>7</b> | Fina  | d Thou  | ughts                                                 | 133 |

|----------|-------|---------|-------------------------------------------------------|-----|

|          | 7.1   | Securit | ty                                                    | 133 |

|          | 7.2   | Future  | e Work                                                | 134 |

|          |       | 7.2.1   | High-level Choices                                    | 135 |

|          |       | 7.2.2   | ILP Optimizations                                     | 135 |

|          |       | 7.2.3   | Traversing the Search Space                           | 137 |

|          | 7.3   | Applic  | ability to Other Applications                         | 138 |

|          |       | 7.3.1   | Generality                                            | 138 |

|          |       | 7.3.2   | Instruction Scheduling for Out-of-Order Architectures | 140 |

|          | 7.4   | Assess  | ment of Contributions                                 | 141 |

|          | 7.5   | Conclu  | nsion                                                 | 143 |

| Bi       | bliog | raphy   |                                                       | 145 |

| Aŗ       | openo | dix A   | Commonly Used Acronyms                                | 157 |

| Aŗ       | openo | dix B   | Additional Tables                                     | 159 |

| Aŗ       | openo | dix C   | Additional Source Code Listings                       | 161 |

| AĮ       | opene | dix D   | "Sandy Bridge" Results                                | 177 |

## List of Tables

| 3.1 | Level 1 cache misses incurred during kernel execution | 39  |

|-----|-------------------------------------------------------|-----|

| 3.2 | Level 2 cache misses incurred during kernel execution | 40  |

| 4.1 | AES-NI Instruction Set                                | 65  |

| 5.1 | GEN1 Simulated Annealing Results                      | 87  |

| 5.2 | GEN1 Results vs. Intel HPL                            | 87  |

| 5.3 | GEN1 vs. Baseline Results                             | 87  |

| 6.1 | AES-GEN Results, CTR mode (cycles/round)              | 103 |

| 6.2 | AES-GEN Results, CTR mode (cycles/byte)               | 106 |

| 6.3 | AES-GEN Results, CBC mode (cycles/byte)               | 112 |

| 6.4 | AES-GEN Results, GCM mode (cycles/byte)               | 117 |

| 6.5 | AES-GEN Results, CCM mode                             | 119 |

| 6.6 | AES-GEN Results for all modes                         | 121 |

| 6.7 | AES-GEN SMT Results for all modes                     | 123 |

| 6.8 | AES-GEN vs. Standard Compiler Results                 | 129 |

| B.1 | ECB finite results for various modes                  | 159 |

| B.2 | ECB-128 finite results with various input sizes       | 159 |

| B.3 | AES-GEN Results, GCM mode using SMT (cycles/byte)     | 159 |

| B.4 | CTR finite results, AES-GEN vs. Intel ASM             | 160 |

| B.5 | CBC finite results, AES-GEN vs. Intel ASM             | 160 |

| D.1 | AES-GEN Results for all modes (Sandy Bridge)          | 177 |

| D.2 | AES-GEN SMT Results for all modes (Sandy Bridge)      | 178 |

# List of Figures

| 2.1 | Generic five-stage processor pipeline                                                                        | 8  |

|-----|--------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Generic superscalar pipeline                                                                                 | 9  |

| 2.3 | SIMD processing                                                                                              | 11 |

| 2.4 | Software pipelining example                                                                                  | 15 |

| 2.5 | Modulo scheduling example                                                                                    | 16 |

| 2.6 | Compiling a Streaming Program                                                                                | 24 |

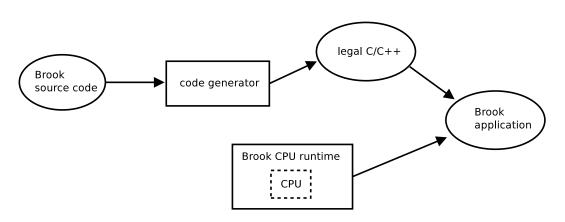

| 3.1 | Compiling a Streaming Program in Brook                                                                       | 30 |

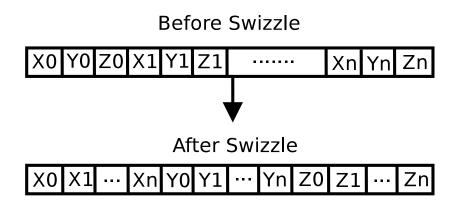

| 3.2 | Data swizzling                                                                                               | 31 |

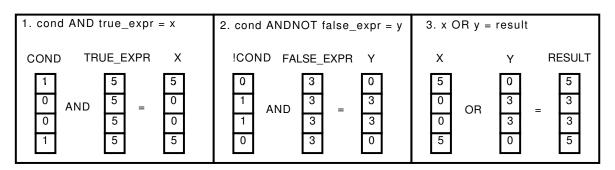

| 3.3 | Conditional assignments in vector mode                                                                       | 35 |

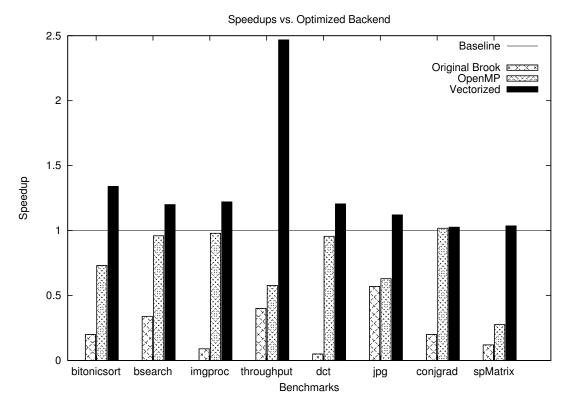

| 3.4 | Autovectorization Experimental Results                                                                       | 38 |

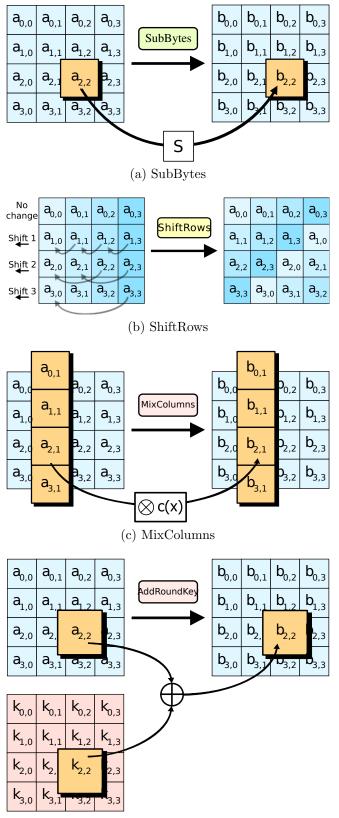

| 4.1 | AES round encryption process                                                                                 | 50 |

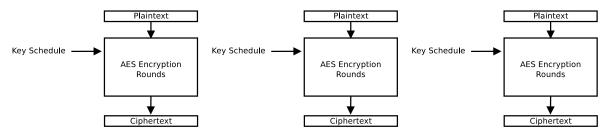

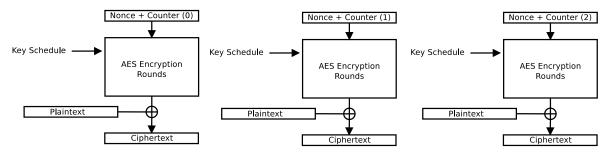

| 4.2 | Electronic Code Book (ECB) mode                                                                              | 53 |

| 4.3 | Counter (CTR) mode $\ldots$ | 53 |

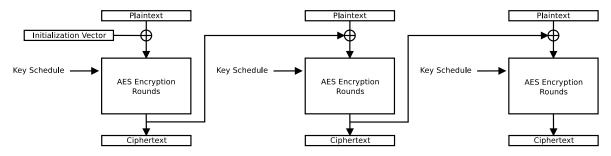

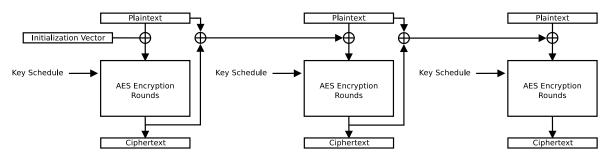

| 4.4 | Cipher-block Chaining (CBC) mode                                                                             | 53 |

| 4.5 | Propagating Cipher-block Chaining (PCBC) mode                                                                | 55 |

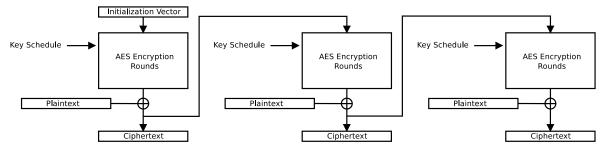

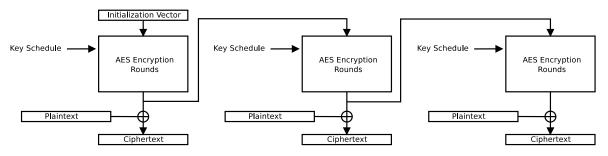

| 4.6 | Cipher Feedback (CFB) mode                                                                                   | 55 |

| 4.7 | Output Feedback (OFB) mode                                                                                   | 55 |

| 4.8 | Galois/Counter Mode (GCM) authentication                                                                     | 57 |

| 5.1 | XOR Tree for CBC Mode                                                                                        | 76 |

| 5.2 | Simulated CTR results with 2 cycle latency on Core 2                                                         | 80 |

| 5.3 | Simulated CTR results with 5 cycle latency on Core 2                                                         | 80 |

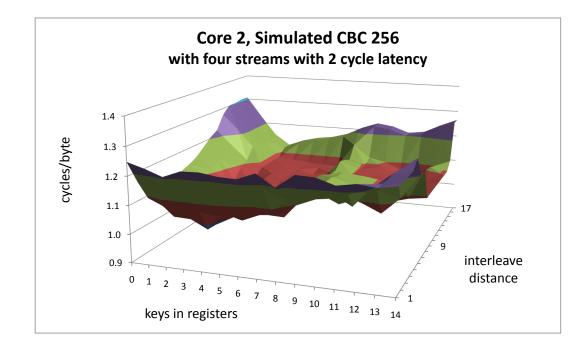

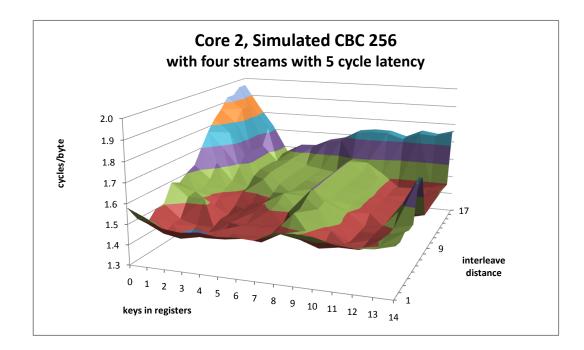

| 5.4 | Simulated CBC4 results with 2 cycle latency on Core 2 $\ldots \ldots \ldots$                                 | 82 |

| 5.5 | Simulated CBC4 results with 5 cycle latency on Core 2 $\ldots \ldots \ldots$                                 | 82 |

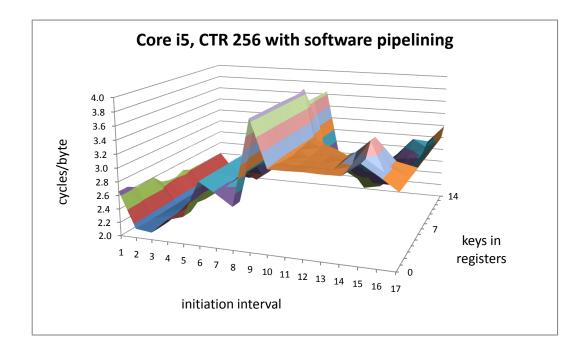

| 5.6 | CTR results on Core i5                                                                                       | 84 |

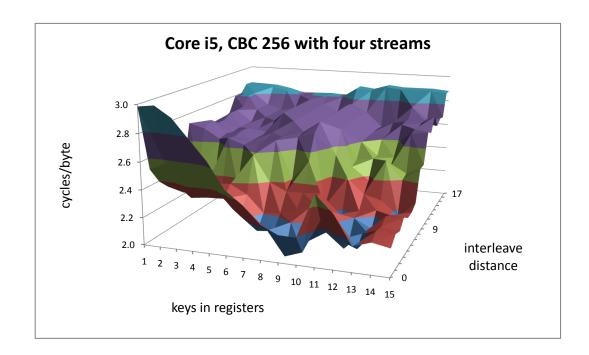

| 5.7 | CBC4 results on Core i5                                                                                      | 84 |

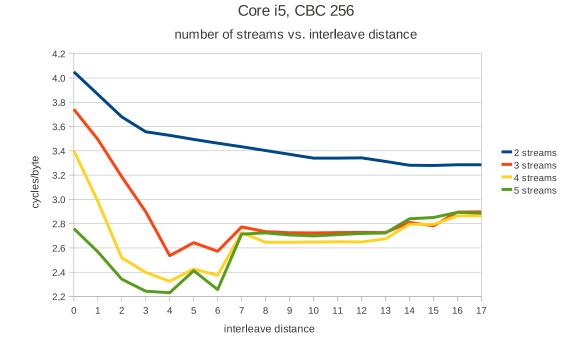

| 5.8 | Results, streams vs. interleaving distance in CBC (Core i5)                                                  | 86 |

### LIST OF FIGURES

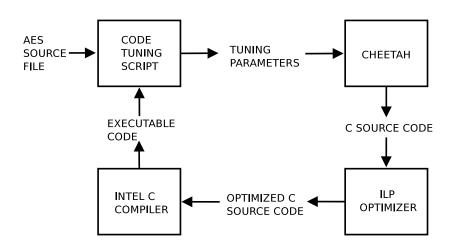

| 6.1  | Structure of the AES-GEN System                 | 95  |

|------|-------------------------------------------------|-----|

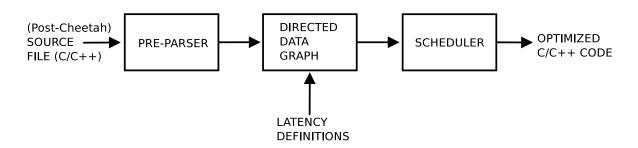

| 6.2  | Structure of the ILP Optimizer                  | 98  |

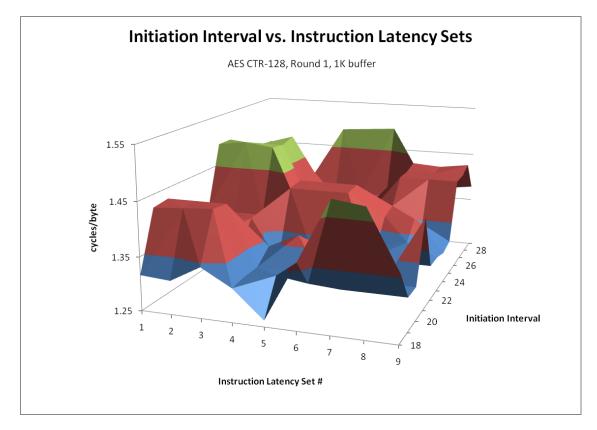

| 6.3  | CTR R1 128, Initiation Interval vs. Latency Set | 101 |

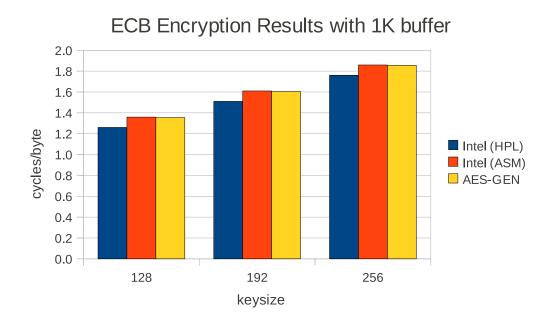

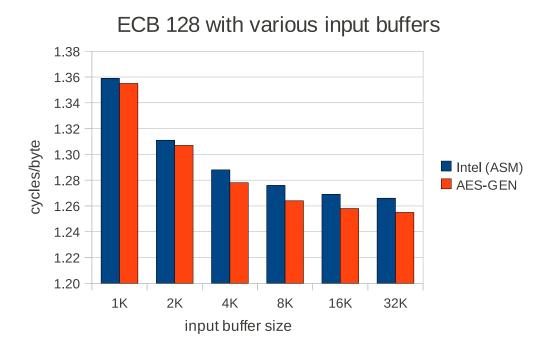

| 6.4  | ECB Results with 1K buffer                      | 108 |

| 6.5  | ECB 128 results with various input buffer sizes | 108 |

| 6.6  | CBC algorithm implementations                   | 111 |

| 6.7  | PCBC algorithm implementations                  | 113 |

| 6.8  | CFB algorithm implementations                   | 114 |

| 6.9  | OFB algorithm implementations                   | 115 |

| 6.10 | GCM 128 Results using SMT                       | 118 |

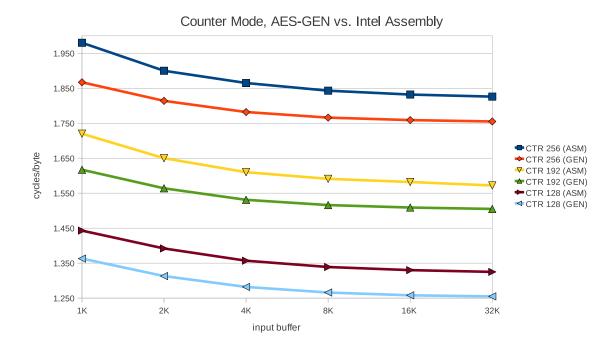

| 6.11 | Counter Results, AES-GEN vs. Intel Assembly     | 126 |

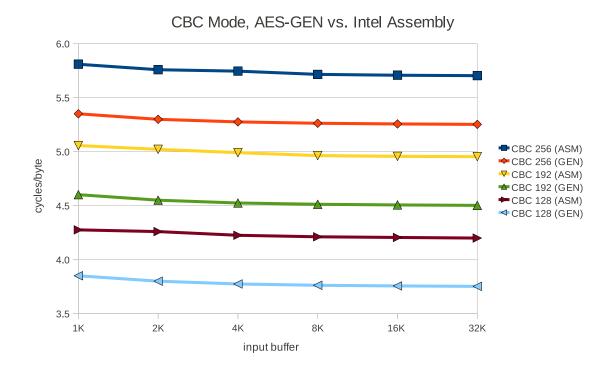

| 6.12 | CBC Results, AES-GEN vs. Intel Assembly         | 127 |

# List of Code Listings

| 2.1 | Simulated annealing pseudocode                                 | 22 |

|-----|----------------------------------------------------------------|----|

| 3.1 | Stream source code, general operations                         | 32 |

| 3.2 | Generated vector code, general operations                      | 33 |

| 3.3 | Stream source code, array lookups                              | 33 |

| 3.4 | Generated vector code, array lookups                           | 34 |

| 3.5 | Stream source code, for-loops 3                                | 35 |

| 3.6 | Generated vector code, for-loops                               | 36 |

| 4.1 | Pseudo-AES code using ECB block cipher mode                    | 18 |

| 4.2 | Using AES-NI in AES-128 CTR mode                               | 35 |

| 5.1 | Using AES-NI in AES-128 CBC mode                               | 59 |

| 5.2 | Interleaving three iterations in CTR mode                      | 70 |

| 5.3 | Software pipelining with an initiation interval of 2           | 72 |

| 5.4 | Interleaving three encryption streams in CBC mode              | 75 |

| 5.5 | Psuedocode of our implementation of simulated annealing        | 77 |

| 6.1 | Cheetah templated AES-128 Counter code                         | 97 |

| 6.2 | Modulo scheduling example, standard CTR                        | 99 |

| 6.3 | AES CTR (round 1) encryption in C using AES-NI instructions 10 | )4 |

| 6.4 | AES CTR (round 2) encryption in C using AES-NI instructions 10 | )5 |

| 6.5 | AES-128 ECB Encryption loop                                    | )7 |

| 6.6 | Strict interleaving four streams of CFB mode 13                | 30 |

| C.1 | Fastest scheduled CTR (round 1) code found by AES-GEN 16       | 31 |

| C.2 | Fastest scheduled CTR (round 2) code found by AES-GEN 16       | 37 |

### Chapter 1

## Motivation

There is no shortage of sensitive information that is transmitted on a daily basis. Medical records, financial transactions, and military communications<sup>1</sup> are all examples of sensitive information that we do not want to freely share with others. To prevent unintended parties from accessing this type of information, encryption is the only answer. Encryption is a vital and necessary component of communicating through several media.

Encryption (or more generally, cryptography) often conjures an image of mathematicians trying to detect patterns in some sort of encrypted text vital to national security. However, modern cryptography actually encompasses several disciplines of study. Mathematical, electrical engineering, and computer science concepts must be combined in order for modern encryption processes to work effectively. As such, the study of modern cryptology surrounding these topics is massive and often appeals to specific fields. Mathematicians are generally concerned with the security and complexity of an encryption algorithm which is referred to as cryptanalysis. Engineers and computer scientists find themselves with the task of implementing these algorithms in hardware and software.

Implementing encryption algorithms on modern architectures has its downside. It can be costly in both time and power requirements. Crucial financial transactions for both investment firms and personal credit card based purchases alike depend on data being encrypted and decrypted as fast as possible for optimal usability. Implementing fast encryption software can be problematic for developers.

The Advanced Encryption Standard (AES) [Daemen and Rijmen, 2002; The National Institute of Standards and Technology (NIST), 2001] is a common and widely used method of encrypting data on computer networks. AES was developed as a suc-

<sup>&</sup>lt;sup>1</sup>or, perhaps more topical: US embassy cables

#### Chapter 1: Motivation

cessor to the Data Encryption Standard (DES), which for many years was the most analyzed, important, and widely used cryptoalgorithm [Smid and Branstad, 1988]. Sequential software implementations of the AES algorithm take large amounts of CPU clock time. The AES algorithm uses repeated byte substitutions, shifts, and bitwise xor operations to encrypt the data. Generalized byte substitutions are difficult to implement efficiently in software. Optimized software implementations combine multiple operations with table lookups. These optimized solutions still require 10 to 14 memory operations to encrypt every byte of data. Due to the importance of using AES, faster implementations are required.

In January 2010, in order implement these costly AES instructions on-chip, Intel released the Westmere microarchitecture that dedicated an instruction-set extension called AES New Instructions (AES-NI) [Gueron, 2010] to its x86\_64 architecture. These instructions have dramatically increased the performance of traditional AES implementations by an order of magnitude. The instructions have high throughput rates, but long latencies. Achieving good encryption performance using these instructions requires the use of hand-tuned assembly libraries. However, relying on assembly libraries has its problems. Assembly implementations are not necessarily optimal for all systems. As new hardware emerges, existing assembly libraries need to be re-evaluated and modified to reflect architectural features. Modifying an algorithm even slightly can require massive changes at the assembly-level and in turn limits exploratory approaches to solving problems. Making both architectural and algorithmic changes to assembly code is incredibly expensive and time-consuming.

With AES-NI being included on new architectures from the world's market share leader of computer microprocessors, opportunities to use local encryption<sup>2</sup> are rapidly increasing. Using AES-NI effectively is rapidly becoming an important problem to solve. Different processor architectural properties greatly affect the performance of AES-NI code. This dissertation presents a program generation system that can build and search many possible AES implementations in a short time-span to find a near optimal solution. Based on the impressive results of this system, it is reasonable to suggest that the scope of these techniques could be widened by further research; the generator could possibly be adapted to optimize other algorithms that use instructionset extensions.

$<sup>^{2}</sup>$ Such as encrypting entire hard-disks, subsections of a hard-disk for private user account files, or compressed file archives.

### 1.1 Thesis

This dissertation argues that using AES-NI instructions effectively is not a trivial process. Current sequentially executing AES-NI based implementations rely too much on the out-of-order architecture to exploit instruction-level parallelism. The thesis of this work is that using a generalized program generator is an effective solution for easily finding near optimal AES implementations that use AES-NI instructions and it serves as a suitable alternative to generating assembly code. We argue that a program generator can accomplish this with three important techniques: (1) making high-level algorithmic changes automatically allows significant opportunities for optimization. Combining these changes seamlessly with traditional optimizations, such as (2) scheduling the AES code to exploit instruction-level parallelism, is a valuable strategy. The program generator also (3) finely tunes arguments that affect (1) and (2) and searches this space using an adapted simulated annealing algorithm that finds a solution quickly. This system allows near optimal AES code to be generated for any base architecture supporting AES-NI in a variety of execution environments<sup>3</sup>.

### **1.2** Contributions

This dissertation makes the following contributions:

- Vector Code Generation In Chapter 3, we find generating vector code is an effective strategy to map streaming languages to general purpose processors. Using a streaming language as a framework to generate vector instructions is a minor, but important contribution. We found that this strategy worked, but allowed us to investigate different systems for code generation.

- AES Program Generation In Chapter 5, we present a program generator that builds CTR and CBC AES implementations. We show this generator can build AES code that performs similarly to hand-coded assembly language libraries. The generator automatically tunes implementations to the underlying architecture.

- Flexible Program Generation In Chapter 6, we present a generalized program generation system that can easily schedule optimized AES code from highlevel source files. We present evidence that using software pipelining and modulo

$<sup>^{3}</sup>$ Execution environments such as sequential execution, encryption using simultaneous multi-threading, or encrypting multiple streams simultaneously

#### **Chapter 1: Motivation**

scheduling can lead to very good schedules and superior performance for parallelizable AES modes.

- Algorithmic Choices We explore the use of automating algorithmic choices through the use of optimizations such as: assigning round keys to registers, setting restrict pointers, adding software prefetch directives, and xor optimizations. These choices make small but crucial changes in encryption runtime. Making these changes manually is difficult if one has to completely reschedule the code. We find applying these algorithmic changes seamlessly with other optimizations is important in achieving best performance.

- Exploiting xor for Cyclic Modes With block ciphers, the plaintext of each block must be added into the key stream at some point. This is done with an xor operator. Xor is both an associative and a commutative logical operation. We propose a novel way of generating AES code that exploits its mathematical properties. Doing this results in a reduction of the dependency chain and allows additional parallelism within the loop body. We also exploit this property at different "levels" within the generation system.

- Function Stitching For function stitched code (like combined encryption/authentication GCM mode), our program generation system can still schedule code effectively. In assembly, function stitching requires merging two assembly functions. Rescheduling two merged functions in assembly code is difficult. We show the ease of finding an optimized schedule in our system by using loop fusion to merge encryption and authentication functions.

- Simulated Annealing Our program generation systems can effectively produce an infinite number of possible AES solutions. With an adapted simulated annealing algorithm, we show that it is a useful code tuning tool to traverse the search space quickly while finding a good solution.

- Assembly Code Alternative The work in Chapters 5 and 6 present two different program generators. In both cases, we find that using a program generator to build AES code is a suitable alternative to writing assembly. This is shown in two ways. First, we are able to generate AES implementations that achieve similar or superior performance compared to reported cycles/byte figures documented by Intel's hand-tuned assembly listings. Secondly, the importance of this contribution is compounded by our inability to reproduce the results reported by Intel, using their assembly listings.

### **1.3 Relevant Academic Publications**

In chronological order, from earliest:

- (1) Mapping Streaming Languages to General Purpose Processors through Vectorization Raymond Manley and David Gregg The 22nd International Workshop on Languages and Compilers for Parallel Computing 2009 Newark, DE, USA Volume 5898 of Lecture Notes in Computer Science, pp. 95–110. Springer Berlin / Heidelberg.

- (2) Code Generation for Hardware Accelerated AES Raymond Manley, Paul Magrath, and David Gregg — 21st IEEE International Conference on Applicationspecific Systems Architectures and Processors(ASAP), 2010 — Rennes, France — pp. 345 –348.

- (3) A Program Generator for Intel AES-NI Instructions Raymond Manley and David Gregg — 11th International Conference on Cryptology in India, Indocrypt 2010 — Hyderabad, India — Volume 6498 of Lecture Notes in Computer Science, pp. 311–327. Springer.

The work in publications listed above was primarily conducted by the author of this dissertation under the supervision of Dr. David Gregg. Additional background research was provided by Paul Magrath in (2). Mike O'Hanlon at Intel Shannon, provided feedback and suggestions for our work in addition to facilitating early access to AES-NI hardware for work done in both (2) and (3). Vinodh Gopal at Intel provided additional feedback on our work in (3).

### **1.4** Dissertation Outline

The title of this dissertation is *Program Generation for Intel AES New Instructions*. The work presented in this document covers topics that relate to the generation of code using instruction-set extensions. Following this introductory chapter, the dissertation continues with a background of architectural features, software ILP optimizations, code generation and streaming languages. Chapter 3 presents work on the automatic code generation for vector instructions for stream applications on general purpose processors. We narrow down the scope of code generation to a single and important problem and an in-depth background and literary survey on AES encryption, block cipher modes, and both software and hardware optimizations for AES is provided in Chapter 4. Chapter 5 presents our first system to generate AES code for both CTR and CBC modes,

using a "static" program generator that both simulates and fully supports AES-NI instructions. Expanding code generation for other AES modes, Chapter 6 presents the generalized AES program generator system that argues our thesis statement. Finally, this dissertation concludes with our final thoughts in Chapter 7. This final chapter contains a critique of our work, future work ideas and an assessment of our contributions. Appendix A contains a glossary of acronyms commonly used throughout this dissertation. Appendix B is attached for "finite" values of graphs found in Chapter 6. Appendix C contains full optimized and scheduled code listings. Appendix D includes AES-GEN performance results when running on a different microarchitecture that supports AES-NI—Sandy Bridge.

## Chapter 2

## Background

This chapter provides background material and literature surveys on the topics necessary to the discussion of the work presented in this dissertation. Namely: Architecture in Section 2.1, Software ILP Optimizations in Section 2.2, Program Generation in Section 2.3, and Streaming Languages in Section 2.4.

### 2.1 Architectural Features

As this dissertation deals with exploiting instruction-level parallelism (ILP) when using high latency instructions through code generation, this section provides background on the architectural features that enable these optimizations. The following techniques that improve ILP deal with an idea that *latency*, or the number of clock cycles an instruction takes to complete, is not uniform for all instructions. In addition, the number of clock-cycles that must elapse before a new instruction can be issued (or the *throughput*) will also affect the amount of ILP that can be exploited on multi-issue architectures.

### 2.1.1 Instruction Pipelining

On multiple-issue architectures, pipelining is a technique that allows machine level instructions to be completed in stages. The number of stages that exist in the pipeline and how the stages are grouped varies for each processor. An instruction will "occupy" a stage in the pipeline, allowing multiple instructions to be executed in parallel.

A new instruction is issued when the instruction currently in the first stage moves on to the second stage and so on. The pipeline stages are designed to be as balanced as possible, or each stage should complete in a unified number of clock cycles. Stages

| Cycle       |    |    |               |                        |                        |                        |                        |     |    |

|-------------|----|----|---------------|------------------------|------------------------|------------------------|------------------------|-----|----|

| Instruction | 0  | 1  | 2             | 3                      | 4                      | 5                      | 6                      | 7   | 8  |

| 1           | IF | ID | EX            | MEM                    | WB                     |                        |                        |     |    |

| 2           |    | IF | ID            | $\mathbf{E}\mathbf{X}$ | MEM                    | WB                     |                        |     |    |

| 3           |    |    | $\mathbf{IF}$ | ID                     | $\mathbf{E}\mathbf{X}$ | MEM                    | WB                     |     |    |

| 4           |    |    |               | $\mathbf{IF}$          | ID                     | $\mathbf{E}\mathbf{X}$ | MEM                    | WB  |    |

| 5           |    |    |               |                        | $\mathbf{IF}$          | ID                     | $\mathbf{E}\mathbf{X}$ | MEM | WB |

Figure 2.1: Generic five-stage instruction pipeline.

are often broken down into several additional stages for instructions that take longer to complete within the pipeline. The number of stages implemented on a processor is influenced by the latency and throughput of its instruction set. While the length of pipelines has gradually increased since their widespread adoption in the 1980s, more stages does not necessarily result in reduction of run-time. The Pentium 4 has a 31 stage pipeline [Hinton et al., 2001], but the Core i7 has reduced this number to 14 [Intel Corp., 2011]. The classic five-stage instruction pipeline [Hennessy and Patterson, 1992] is shown in Figure 2.1 with the following stages:

- 1. (IF) Instruction Fetch Instructions are fetched from the cache.

- 2. (ID) Instruction Decode Instructions are decoded in divided into parts needed for execution.

- 3. (EX) Execute Now decoded, instructions execute and take a variable number of cycles to complete, depending on type of instruction.

- 4. (MEM) Memory Operations This stage accommodates long-latency memory operations if the executing instruction needs to fetch data.

- 5. (WB) Write-back Write results of the instruction back to memory.

More complex pipelines are sometimes designed with additional stages to accommodate instruction-set extensions to the architecture. For example, this dissertation mentions the **aesenc** instruction multiple times which has a 2 cycle throughput and a 6 cycle latency on the Intel Westmere processor [Akdemir et al., 2010]. For this to work, multiple stages must exist to allow for possibly three of these instructions to execute in parallel. While a pipeline has the ability to execute multiple instructions in parallel, data dependency between instructions will cause the pipeline to *stall*. On in-order processors, if an instruction is held up in a particular stage, the processor must wait to push instructions down the pipeline. This stall wastes clock cycles while the processor waits to complete the instruction. Stalls are caused by structural stalls, control stalls, or data stalls. Structural stalls happen when a multiple instructions require the same processor resource. Control stalls occur with conditional statements that could change the target of the following instruction. Branch predictors try to prevent these stalls. Data stalls occur when an instruction has a data dependency on another instruction already in the pipeline. The instruction cannot continue until its predecessor completes executing. There are a number of possible solutions to prevent and/or limit these pipeline stalls. However, limiting data stalls are of particular interest to us<sup>1</sup>.

|             | Cycle |    |                        |                        |                        |                        |               |     |    |

|-------------|-------|----|------------------------|------------------------|------------------------|------------------------|---------------|-----|----|

| Instruction | 0     | 1  | 2                      | 3                      | 4                      | 5                      | 6             | 7   | 8  |

| 1           | IF    | ID | $\mathbf{E}\mathbf{X}$ | MEM                    | WB                     |                        |               |     |    |

| 2           | IF    | ID | $\mathbf{E}\mathbf{X}$ | MEM                    | WB                     |                        |               |     |    |

| 3           |       | IF | ID                     | $\mathbf{E}\mathbf{X}$ | MEM                    | WB                     |               |     |    |

| 4           |       | IF | ID                     | $\mathbf{E}\mathbf{X}$ | MEM                    | WB                     |               |     |    |

| 5           |       |    | $\mathbf{IF}$          | ID                     | EX                     | MEM                    | WB            |     |    |

| 6           |       |    | IF                     | ID                     | $\mathbf{E}\mathbf{X}$ | MEM                    | WB            |     |    |

| 7           |       |    |                        | IF                     | ID                     | EX                     | MEM           | WB  |    |

| 8           |       |    |                        | $\mathbf{IF}$          | ID                     | $\mathbf{E}\mathbf{X}$ | MEM           | WB  |    |

| 9           |       |    |                        |                        | IF                     | ID                     | EX            | MEM | WB |

| 10          |       |    |                        |                        | IF                     | ID                     | $\mathbf{EX}$ | MEM | WB |

Figure 2.2: Generic superscalar pipeline.

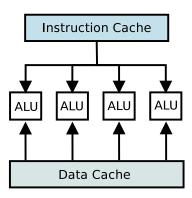

### 2.1.2 Superscalar

Instructions on a single-issue scalar processor execute sequentially and process one or two operands. Functional units that are not needed while the current instruction is being executed remain idle when they could be doing something useful. Superscalar architectures were designed to improve instruction scheduling by dispatching instructions to idle functional units. A superscalar architecture is a multiple-issue processor

<sup>&</sup>lt;sup>1</sup>As we will see in Chapter 4, the AES algorithm is a block-cipher that has a chain of dependent encryption rounds and executing these rounds will cause data stalls.

#### Chapter 2: Background

which implements a form of instruction-level parallelism by executing more than one instruction at a time on different functional units. Figure 2.2 shows a superscalar pipeline that fetches and executes two instructions at a time.

Using a superscalar pipeline allows the CPU to have greater throughput than its clock speed would suggest and would normally process more than one instruction per clock cycle. The ability to parallelize at this level depends on several factors. One such factor is the number and types of functional units. Different functional units can process different types of instructions. For example, given a processor has a functional unit that can process integer and float operations and a functional unit that can process integer and memory operations, two integer operations could be completed in parallel, whereas two sequential float instructions would cause a stall. The data dependency between instructions is also checked by the hardware at run time to ensure that programs execute properly. This is a important limitation of superscalar hardware to note, as other optimization techniques must be exploited in these instances.

### 2.1.3 Simultaneous Multithreading

Research has shown that superscalar architectures are limited at saturating the available resources (functional units) with multi-issue processors [Eggers et al., 1997]. Simultaneous multithreading (SMT) is a modern architectural feature on superscalar CPUs that implements hardware multithreading by permitting independent threads of execution in an effort to better utilize processor resources. To do this, instructions are issued from independent threads to multiple functional units. While increased resources are required to fetch instructions from multiple threads and keep thread information, the use of SMT will theoretically allow instructions from different threads to be used by idle parts of the processor. This is why SMT is implemented on a superscalar processor. This technique is very similar to superscalar pipelines but with multiple instruction queues to fetch from.

Work by Tullsen et al. [1995] showed that SMT has potential to increase resource usage on single-chip multiprocessors. They compared SMT to single-chip multiprocessing. While the two systems have similar organization layouts—both have their own set of registers, multiple functional units, and high issue-bandwidth—they have a very different strategy for partitioning and scheduling resources. Multiprocessing issues instructions to a fixed number of functional units to complete each thread. SMT can change this assignment every cycle. This allows for more efficient use of functional units.

On Intel processors since the Pentium 4 (and including the ones used for experiments

Figure 2.3: SIMD example, a single instruction is applied to multiple data.

found in this thesis), hyper-threading is the term used for Intel's SMT implementation [Intel Corp., 2011]. Intel implements SMT by addressing two virtual or logical processors for every one physical processor. It is possible to pin a process to one of these virtual processors, but this remains transparent to the operating system. The hardware does this so the operating system can think it is scheduling multiple processes simultaneously on "different processors", allowing the processor to send instructions down the pipeline from multiple threads. This limits structural stalls.

### 2.1.4 Vector/SIMD

SIMD (Single Instruction, Multiple Data) is a technique employed to achieve data level parallelism. On modern architectures, SIMD serves as a vector processor. In SIMD computer architecture [Flynn, 1972], the computer exploits multiple data streams against a single instruction stream in order to perform operations that may be easily parallelized. This is shown in Figure 2.3. By processing multiple data elements in parallel, SIMD processors provide a way to utilize data parallelism in applications that apply a single operation to all elements in a vector.

The idea behind SIMD programming is that one can perform the same action on several elements in parallel. On general purpose processors, the "vector processor" comes in the form of extensions to the instruction set architecture (ISA). For example, an instruction-set extension (ISE) on the x86 architecture is Streaming SIMD Extensions (SSE) [Intel Corp., 2011]. Other processors also have vector processing ISEs, such as: AltiVec for the PowerPC architecture [Freescale Semiconductor, 1999] and VIS on UltraSparc [Kohn et al., 1995]. SSE is a SIMD instruction set extension to the x86 architecture. SSE has access to eight 128-bit registers. The 64-bit extension to the x86 architecture (x86\_64), adds an additional eight vector registers to use. XMM0 through XMM15 can be accessed in 64-bit operating mode, while only XMM0 through

#### Chapter 2: Background

XMM7 can be accessed in 32-bit operating mode. Other generations of SSE have been added to current x86 architectures. The latest iteration of SSE is version 4.2 which was released in 2009.

#### Intrinsics

Compilers are limited in applying vectorization from high-level code without additional annotations. While writing assembly-level vector instructions can be done, a set of macros called *intrinsics* exist to allow high-level language programmers to make use of SIMD instructions. Intrinsics are written as high-level language functions that often have a 1:1 correspondence to their assembly level counterparts. Code that uses intrinsics can also benefit from further low-level optimizations applied by a highlevel language compiler as he compiler will manage register allocation and instruction scheduling. Instrinsics are also used in source-to-source translators and code generators that attempt to automatically vectorize code.

### 2.1.5 Autovectorization

While it is relatively easy to incorporate the advantage of using vectors while writing code on the assembly level, automatically generating vector code from high-level languages remains a serious challenge. Data dependency and loop analysis are key research points in vectorization [Wolfe, 1990; Allen and Kennedy, 1987]. Current autovectorization techniques are generally limited to transforming loops when a number of requirements are known and/or met. For example, gcc requires several conditions to be met in order to vectorize loops [Naishlos, 2004; Nuzman and Zaks, 2006]. If values of successive iterations of a loop are dependent on its predecessor, data dependency prevents the vectorization of loops. Data alignment becomes a problem as vector registers generally require data to be aligned to a specific boundary (most commonly quad-word). Interleaved data (found in user defined structures) also causes data-alignment issues. Control-flow structures, such as if statements, are difficult to vectorize as conditionals may affect only some elements currently loaded into a vector. Many autovectorization techniques are not implemented by stand-alone compilers. Autovectorization is often more effective when tuning for specific algorithms where memory boundaries and conditional flow in loops are known. Autovectorization is a combination of both hardware and software ILP optimization techniques.

### 2.2 Software ILP Optimizations

Hardware mechanisms to improve instruction-level parallelism can only go so far. For in-order architectures, exploiting ILP depends entirely on the compiler. Preventing stalls in the pipelines on superscalar machines depend on the sequence of instructions and which resources they wish to use. Both in-order and out-of-order execution architectures can benefit from high-level code that encourages standard compilers to exploit ILP in software using different *instruction scheduling* techniques.

### 2.2.1 Instruction Scheduling

Compilers use instruction scheduling to expose more instruction-level parallelism for superscalar architectures. On in-order architectures, the compiler uses instruction scheduling to re-arrange the operations into groups that can be independently executed. A simple but effective *list scheduling* algorithm can be applied to a basic block to create the independent groups and this can result in a near optimal scheduling solution [Lawler et al., 1987]. Groups are created by building a data dependence graph (DDG), in which operations are represented by nodes with directed edges that show dependencies between the operations. Exploiting ILP when scheduling basic blocks which execute repeatedly is an important problem.

### 2.2.2 Loop Unrolling

The majority of running time in most programs is spent iterating over a loop or several loops. Until recently, with the advent of streaming languages for example, the basic blocks of loops are usually not written to be executed in parallel in a high-level language. Usually, the iterations of the loop can be executed in parallel, and loop unrolling is a common way to exploit ILP. This allows out-of-order architectures to execute instructions from several iterations of the loop body that is likely to be subject to flow-dependency in single iterations. Unrolling is an easy optimization to implement in compilers and existing compilers apply it to loops to great effect [Lowney et al., 1993]. However, unrolling loops do have some drawbacks. Unrolling means more code and code growth can be a sensitive issue in things like embedded processors. Unrolling also suffers based on the degree of unrolling. If loops are unrolled by a degree that is not evenly divisible by the number of iterations, a scalar "clean-up" loop is necessary to execute remaining iterations. With small loops, this can seriously affect any speedup potential. With these drawbacks in mind, there is a technique that can solve both these problems while continuing to exploit ILP.

### 2.2.3 Software Pipelining

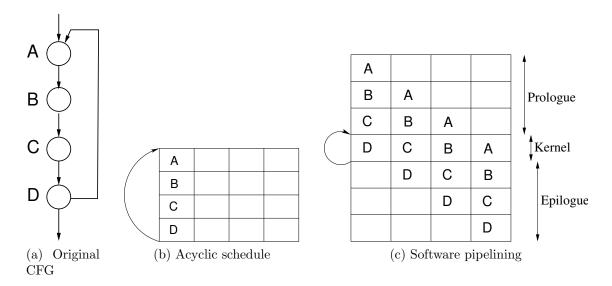

Software pipelining is an instruction scheduling technique that takes instructions from several loop iterations and combines them to build a new, parallelized basic block [Lam, 1988]. Figure 2.4 shows how code from a simple loop is scheduled using software pipelining. In Figure 2.4a, the control flow graph representation shows a loop with four statements. Using an acyclic schedule (shown in Figure 2.4b), the statements are executed sequentially. In Figure 2.4c, software pipelining is applied to the loop and the four statements are scheduled to execute simultaneously, exploiting ILP. This is achieved by breaking down software pipelining into three stages:

- 1. The *prologue* contains all instructions that are required to be executed before the instructions of the current loop that will be included in the loop body.

- 2. The loop body is referred to as the kernel or *steady state*, as once the program reaches this point, this body of code will repeat until it must exit. The kernel contains all instructions needed to complete one iteration of the loop, but as instructions will be from different iterations, they can be scheduled in parallel.

- 3. When the kernel finishes executing, some loop iterations are still live. The *epi-logue* consists of code required to finish these iterations correctly.

While Figure 2.4 shows a simple four statement loop body, the number of statements from each iteration included inside the steady state needs to be flexible. It might be pertinent to allow long-latency instructions to be scheduled further down the pipeline, or across several kernel stages. Low-latency instructions may be grouped together and executed in a single pipeline stage. The "length" of the kernel is measured in machine cycles and is known as the *initiation interval* (*ii*). This value can be adjusted to exploit different levels of ILP. The *ii* sets the throughput of the pipeline.

The use of the three stages creates tighter ILP schedules while solving the problem of code growth and the need for a clean up loop. While software pipelining expands code, the growth is quite small in comparison to unrolling and affects performance less. Stifling code growth within the loop is the most important [Rau, 1994] and the software pipelining kernel is the same size as the original loop body. However, for multiple iterations to be executed the same loop body, variable renaming and copies must be included [Lam, 1988] to send data from one loop iteration to the next. This

Figure 2.4: Software pipelining example. Images taken from [Gregg, 2001]

can increase register pressure, but the variables created by the renaming and copy instructions can be optimized out at compile time.

The prologue and epilogue also contribute to code growth, but the amount is dictated by how many loop iterations exist in the kernel. Inherently, the instructions in both stages can also be out-of-order which benefits during global instruction scheduling. Compilers can unroll loops to high degrees, causing an inflated number of instructions scheduled and this increases compensation code which is needed to support the overlapped iterations. Software pipelining also does not require an expensive clean up loop, as the epilogue finishes the loop cleanly.

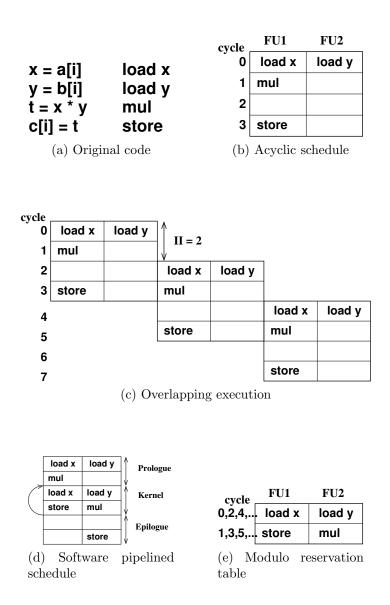

### 2.2.4 Modulo Scheduling

The initiation interval determines how a software pipelining kernel is built. From our experience, we used *ii* slightly differently in Chapters 5 and 6. In Chapter 5, the throughput is measured in number statement lines without any regard to what their corresponding throughput and latency would be at the machine level. In Chapter 6, we can assign specific values to each statement in the graph and *ii* value will schedule them accordingly. The approach we used to build our software pipelined loops in Chapter 6 is called *modulo scheduling* [Rau and Glaeser, 1981]. Modulo scheduling is a method of implementing software pipelining in loops that do not contain branches that produces good code while minimizing code growth.

Figure 2.5 shows how code from a simple loop would be pipelined using modulo scheduling. In Figure 2.5a, the original source code shows a loop body that loads two

Figure 2.5: Modulo scheduling example. Images taken from [Gregg, 2001]

values from separate arrays, multiplies these values together, and stores the result into a third array. Given that the load and store instructions take one cycle each and the multiply takes two cycles, the acyclic schedule for this loop on a processor with two functional units is scheduled as seen in Figure 2.5b. There is no cyclic dependency from one iteration to the next; each iteration completes in four cycles and successive iterations can be overlapped and execute in parallel as shown in Figure 2.5c using an *ii* value of 2. Figure 2.5d, shows the software pipelined schedule of the loop. The prologue contains the first three instructions. The kernel then contains the loads of x[i+1] and y[i+1] executes mul on those values while the previous iteration's mul instruction finishes and stores the value in t[i] before the loop continues. The epilogue then contains the clean up code, which in this case is a store. The order in which these instructions execute is listed in Figure 2.5e. While software pipelining and modulo scheduling are very effective techniques for instruction scheduling, they are many other methods to optimize entire algorithms or programs and is sometimes done with a *program generator* (or *code generator*).

### 2.3 Program Generation

The origin of early code generators were "superoptimizers" and "peephole optimizers". The scope of these optimizers were limited to small programs or sections of a program to reduce the number of instructions in a program through instruction selection, constant folding, and removing redundant code. Massalin [1987] created a "superoptimizer" to find the fewest instructions required to compute a given function. However, the author states that often this technique is only practical for programs that have 13 machine instructions or less, and the effectiveness is largely dependent on the target architecture (and which instructions are available). Peephole optimizers were often integrated into code generators. Davidson and Fraser [1984] described techniques on how to automatically generate peephole optimizations using a description of the underlying architecture. Fraser and Wendt [1988] extended this work to integrate a set of peephole optimizations with a naïve code generator to create an automatic code generator and optimizer that could be retargetted to different architectures with minimal effort.

The scheduling optimizations listed in the previous section are solutions that, when applied, are optimized for a given architecture. As the architectural features change for new processors, the scheduling optimizations will often need to be recalculated for optimal (or near-optimal) performance. Scheduling is also not the only optimization that must be considered when compiling for a different platform. When presented

#### Chapter 2: Background

with the challenge of optimizing an algorithm, many optimization techniques need to be considered. A system that considers these architectural or algorithmic changes, and generates an optimized version of the code is called a program generator.

Iterative program generators take a piece of code and try to find the fastest version by trying combinations of different techniques to optimize the code, just like a programmer would by hand. The difference is that a code generator does not have to make guesses like a programmer would. An iterative program generator can try all the conceivable combinations of the optimization techniques to find the best solution. The lack of user intervention is convenient and cost saving. The work involved in optimizing even a small piece of code can take weeks by hand. A code generator can generate all the combinations possible almost instantly. While it completes a time-consuming search for a solution, it requires no attention. In exchange for this one expensive search, the time saved by running a faster version of the code on a continual basis is desirable.

### 2.3.1 Domain Specific Code Generators

There are several well known code generators (also referred to as library generators) that focus on a particular subset of problems. One of the most successful code generators is Fastest Fourier Transform in the West (FFTW) [Frigo et al., 2005; Frigo and Johnson, 1998]. It is a library for computing the discrete Fourier transform (DFT) and is designed to adapt to hardware features to maximize performance. It is able to tune code for machine-specific instruction-set extensions, like SIMD, and uses a specialized compiler to generate optimized implementation of discrete cosine and sine transforms from the parent DFT algorithm. The DFT algorithm can be of real- or complex-type valued arrays of varied size and dimensions. Depending on these defined algorithmic properties and the underlying architecture, the derived DFT algorithm could work very differently from machine to machine.

FFTW generates this code in two parts. The FFTW planner (the code generator) is invoked and the user must specify the shape of the input data (type values and array dimension sizes) of the problem to be solved. The planner measures the actual run time of many different plans and returns the fastest. This is often a time-consuming process but as DFTs are computationally expensive, it is often worth while for "performance-critical" applications. Without getting into the mathematics behind DFTs, FFTW solves a problem first by reducing the defined vector rank of a DFT to a single (possibly multi-dimensional) DFT. This single DFT must then be reduced to a sequence of one-dimensional DFTs. These one-dimensional DFTs are then solved by a known DFT algorithm. Since these steps can be executed out of order and/or interleaves, searching a

series of plan-permutations eventually returns a "correct" plan. These transformations yield various solutions that will nest loops differently with varying vector sizes and so on. The cost to compute the DCT given these high-level code constructs is calculated given the architectural properties. This is how a "correct" plan is determined.

Whaley et al. [2000] presents a code generator called ATLAS, which generates linear algebra routines and focuses the optimization process on the implementation of matrix multiplication. Like the FFTW planner, the parameter values of a matrix multiplication implementation influence how the code is generated. The generator tries multiple values for the tile size and loop unrolling degrees and evaluates the costs of the various configurations. The almost exhaustive search proceeds by generating different versions (different sizes) of matrix multiplication that are dependent on the input values.

SPIRAL, or Signal Processing Implementation Research for Adaptable Libraries, is another code generation library. SPIRAL can generate code for several subsets and formulae associated with digital signal processing (DSP), such as linear transformations [Püschel et al., 2005]. Through SPIRAL, researchers have investigated the use of automatic vectorization of both the Discrete Fourier Transform (DFT) [Franchetti and Püschel, 2003] and the FFT [Franchetti and Püschel, 2007].

In those works, Franchetti and Püschel discuss the difficult process of exploiting SSE instructions on scalar code. In addition, they also mention the problem of finding an optimal solution when generating code for a target architecture. They offer a specific dynamic programming search to find a "good match" between the formula space and architecture it is being mapped to. Of more direct relevance is their work on the SPL compiler [Xiong et al., 2001]. The SPL compiler, developed for SPIRAL is a system that uses formula transformations and intelligent search strategies to create optimized DSP libraries.

#### 2.3.2 Traversing the Search Space

As mentioned earlier, early code generators had a limited scope for optimization. Instruction sets were smaller and "useful programs" were about a dozen machine instructions long. With Massalin [1987]'s superoptimizer, he considered that it was feasible to exhaustively search every possible program. However, he concedes that the search grows exponentially with each additional instruction.

Frigo et al. [2005] states that finding a correct plan can be a very time-consuming process for FFTW. FFTW and ATLAS can both use exhaustive searches as their search spaces are finite, but code generators often have to traverse a search space which rapidly

#### Chapter 2: Background

expands with small options that can be turned on and off that may or may not improve the code depending on another option's state. Consider the optimization flags that could be passed to gcc alone. The resulting possibilities of a complex program could be in the billions. There needs to be a way to search the search space more efficiently because exhaustively trying all combinations is rarely computationally feasible. Several techniques have been developed to traverse these vast search spaces.

PEAK is a system introduced by Pan and Eigenmann [2006b] which considers a feedback-directed approach to making the most use of 38 of gcc's on/off optimization flags<sup>2</sup>. They find solutions quickly (in comparison to other iterative compilation techniques) by creating program "sections". PEAK detects which parts of the program could benefit from optimization and places them into a "section". The system then profiles each applies compiler optimizations independently to these sections. Once each section is tuned, the program is compiled and given to the user. To traverse the exponential search space, they apply an algorithm called combined elimination [Pan and Eigenmann, 2006a]. This algorithm combines several ideas to reduce the search space. It first identifies which optimizations increase runtime. Then it iteratively tries to eliminate each negative-optimization one at a time. The authors claim similar performance gains can be achieved from a search that takes several minutes, as opposed to a few hours.

Related work by Hoste and Eeckhout [2008] attempts to find the best gcc optimizations again amongst an even greater search space<sup>3</sup>. Their system, Compiler Optimization Level Exploration (COLE), uses a multi-objective search based on an evolutionary algorithm to adjust for code size, code quality, and/or compilation time. Acovea is a tool developed by Ladd [2009] that uses genetic algorithms to find the best options when compiling a program with gcc. Similar ideas have been proposed for code generators.

Work on using machine-learning algorithms to find the best general compiler options when tuning code for a particular target has also been investigated. Li et al. [2005] used SPIRAL to demonstrate the power of using machine learning techniques in automatic algorithm selection and optimization. Li et al. argue that while generators like SPIRAL and FFTW can find near-optimal performance for a particular machine just by using empirical searches, these algorithms have only been shown to work without considering the characteristics of input data. By using genetic algorithms and a classifier system that consider and adapt specifically to input data, Li et al. are able

<sup>&</sup>lt;sup>2</sup>These options create  $2^{38}$  combinations, and are used in their experiments.

<sup>&</sup>lt;sup>3</sup>The authors state a search space of greater than  $2^{60}$ .

to increase performance of classic sorting algorithms. They argue that using a genetic algorithm is necessary because the deep cache hierarchy and complex architectural features in modern systems are not considered when studying the complexity of sorting algorithms.

The MILEPOST GCC project [Fursin et al., 2008] also uses machine learning during the gcc compilation process for a broader range of inputs and hardware targets. What is unique about their approach is that gcc may be used to compile any program that could target a number of different platforms. As such, the machine learning compiler they describe can automatically adjust its optimization heuristics to make applications faster, reduce the code size, or even the compilation time. To train the machinelearning algorithm, they use a set of 500 random sequences that each applied a range of compiler flags turned on and off to a benchmark. They found that while being a time-consuming process, this training pass worked effectively to build other code when run on a particular architecture.

Expanding on the MILEPOST project, Leather et al. [2009] presented work that automatically finds "features" of a given program that are likely to be improved by the machine-learning techniques. It sends feature data to the machine learning tool and in return, influences the genetic algorithm. Tournavitis et al. [2009] extended work on MILEPOST as well by adapting machine-learning to generating auto-parallelized code. The authors argued that weaknesses exist in traditional parallelizing compilers (such as autovectorizing compilers—see Section 2.1.5). They found that adapting the learning techniques to this problem found more code that could be parallelized compared to that found by other automatic tools. The work far exceeds other tools and comes close to performance of manually parallelized code, such as manually tuned OpenMP.

The heuristic methods mentioned this section are based on genetic programming approaches, decision trees, and the *k*-nearest neighbours classifier to perform machine-learning. There are other methods of traversing a search space without narrowing the scope. One such algorithm is simulated annealing.

#### 2.3.3 Simulated Annealing

Simulated annealing is a heuristic search algorithm that employs probabilistic reasoning to increase the search space [Aarts and Korst, 1988; Skiena, 1998]. It increases the search space by allowing for occasional steps in the wrong direction by jumping to inferior solutions. This jump is random based on the current "temperature". The transition probability from solution<sub>i</sub> to solution<sub>j</sub> (where  $s_i$  and  $s_j$  are defined as the cost of each solution) at temperature T is defined as:  $P(s_i, s_j, T) = e^{(s_i - s_j)/(k_B T)}$  where

| Listing 2.1: | Simulated | annealing | pseudocode. |

|--------------|-----------|-----------|-------------|

|--------------|-----------|-----------|-------------|

```

Simulated Annealing()

1

Create initial solution S

2

Initialize temperature t

3

repeat

4

for i = 1 to iteration-length do

5

Generate a random transition from S to S[i]

6

if (C(S) \ge C(S[i])) then S = S[i]

7

else if (e^{(C(S) - C(S[i]))}/(k*t)) > random[0,1)) then S = S[i]

8

9

Reduce temperature t

10

until (no change in C(S))

Return S

11

```

$k_B$  is Blotzmann's constant. Using simulated annealing has been found to be an effective solution for graph partitioning and traveling salesman problems<sup>4</sup>[Kirkpatrick, 1984].

This equation is used in the simulating annealing algorithm to accept or reject the current solution. The solutions are evaluated by a cost function. In the beginning, the search can and should be quite erratic in direction, but always testing a neighbouring solution. One of the ideas behind simulated annealing is that bad solutions are accepted earlier in an effort to prevent the search from being stuck in local minima. As the search goes on, the probability of accepting bad solutions reduces. This is done through a temperature variable that "cools down" when progress is made. Once the temperature is fairly low, the algorithm suggests that it has found a good solution and is more likely to test solutions closer to the "good" solution.

Finding a practical cooling solution requires a trial-and-error approach and needs to be tailored for the cost function used (function C(S) in Listing 2.1). This function evaluates the solution and returns a value or cost. The temperature variable itself cools down exponentially after every set number of iterations. The temperature rapidly cools because good solutions are starting to become evident. Solutions will always be accepted if the cost of the current solution is lower than the cost of the previous solution. In addition, the probability function noted above is compared against a random value between 0 and 1. If it the probability function is greater than the random number, then the solution is accepted regardless of cost. A general outline of the simulated annealing algorithm is shown with pseudocode in Listing 2.1.

<sup>&</sup>lt;sup>4</sup>In Chapters 5 and 6, we use simulated annealing to find solutions among a search space that is computationally infeasible to search exhaustively.

## 2.4 Streaming Languages

As discussed in the previous section, using a program generator can be a way to expose parallelism in a program. However, some algorithms have properties that are simple and straightforward enough to benefit from a set of optimizations geared for parallel processing. The essential idea of stream processing is that large quantities of data are brought into local memory, manipulated with a single or very few instructions, stored back into memory and then are unlikely to be used again. An example of this type of application<sup>5</sup> is presented in work by Manavski [2007], in which they implement the AES encryption algorithm using a stream language. This programming paradigm has been implemented in a series of *streaming languages* designed to easily exploit parallel processing. Streaming languages were originally (and concurrently) developed for specialized streaming processors, such as RAW [Taylor et al., 2004] and Imagine [Khailany et al., 2001]. Stream processing then found a home on the more commonly found graphics card (GPU) through CUDA [NVIDIA, 2007] and gaming processors, such as the Cell BE [Zhang, 2007], which led to the idea that streaming languages could provide the necessary structure to effectively map their code onto general-purpose processors. More recent streaming efforts like OpenCL [Munshi, 2009] have partnered several corporate entities to develop an open standard for specifying these languages.

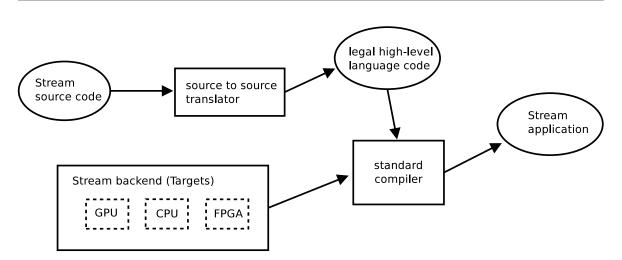

Streaming languages are often defined very differently. They can be developed as simple libraries that target a specific processing unit. Rapidmind [Monteyne, 2008] (and later, Intel Array Building Blocks Intel Corp. [2010b]) do this for GPPs. CUDA specifically targets NVIDIA GPUs. OpenCL tries to optimize stream processing by targeting both GPPs and GPUs simultaneously. Some streaming languages, such as Brook [Buck et al., 2004], are defined by simply extending a more familiar language such as C/C++. Others, like StreamIt [Thies et al., 2002], were created with the belief that an entirely new language is essential to representing the stream model. Both platforms share common attributes such as facilities to read and write stream data, kernels (or filters), and control techniques such as reductions. *Kernels* are defined as the function that operates on all elements of a stream. Both platforms also have a compiler to generate code and a runtime (or back-end) to serve as the computational engine. Figure 2.6 shows the general process of compiling a stream program with Brook and Streamit.

The *computational intensity* property of streaming is represented by a kernel. Kernels operate on every element in the stream and are the only place individual stream

$<sup>^5\</sup>mathrm{And}$  an application important to this dissertation

Figure 2.6: General Process of compiling a Streaming Program in Brook and Streamit.

elements can be accessed. It is usually required that streams be initialized and written back out to normal arrays to keep the streams separated between the main body of the program and kernels. In Brook, this is done with a set of runtime functions called **streamRead** and **streamWrite**. It ensures that the language implementation is in complete control of the data structures.

When compiling streaming code, a source-to-source translation is commonly used on the source with resulting output in another high-level language [Das et al., 2006; Amarasinghe et al., 2005]. This allows the C++ compiler to apply low-level optimizations. When translating the kernels, a loop is generated to iterate through the size of the input stream(s). The code contained within the kernel function is then evaluated within the loop for every single element of the stream. Further optimizations are applied, dependent on the target architecture.