### LEABHARLANN CHOLÁISTE NA TRÍONÓIDE, BAILE ÁTHA CLIATH Ollscoil Átha Cliath

### TRINITY COLLEGE LIBRARY DUBLIN The University of Dublin

#### Terms and Conditions of Use of Digitised Theses from Trinity College Library Dublin

#### **Copyright statement**

All material supplied by Trinity College Library is protected by copyright (under the Copyright and Related Rights Act, 2000 as amended) and other relevant Intellectual Property Rights. By accessing and using a Digitised Thesis from Trinity College Library you acknowledge that all Intellectual Property Rights in any Works supplied are the sole and exclusive property of the copyright and/or other IPR holder. Specific copyright holders may not be explicitly identified. Use of materials from other sources within a thesis should not be construed as a claim over them.

A non-exclusive, non-transferable licence is hereby granted to those using or reproducing, in whole or in part, the material for valid purposes, providing the copyright owners are acknowledged using the normal conventions. Where specific permission to use material is required, this is identified and such permission must be sought from the copyright holder or agency cited.

#### Liability statement

By using a Digitised Thesis, I accept that Trinity College Dublin bears no legal responsibility for the accuracy, legality or comprehensiveness of materials contained within the thesis, and that Trinity College Dublin accepts no liability for indirect, consequential, or incidental, damages or losses arising from use of the thesis for whatever reason. Information located in a thesis may be subject to specific use constraints, details of which may not be explicitly described. It is the responsibility of potential and actual users to be aware of such constraints and to abide by them. By making use of material from a digitised thesis, you accept these copyright and disclaimer provisions. Where it is brought to the attention of Trinity College Library that there may be a breach of copyright or other restraint, it is the policy to withdraw or take down access to a thesis while the issue is being resolved.

#### **Access Agreement**

By using a Digitised Thesis from Trinity College Library you are bound by the following Terms & Conditions. Please read them carefully.

I have read and I understand the following statement: All material supplied via a Digitised Thesis from Trinity College Library is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of a thesis is not permitted, except that material may be duplicated by you for your research use or for educational purposes in electronic or print form providing the copyright owners are acknowledged using the normal conventions. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone. This copy has been supplied on the understanding that it is copyright material and that no quotation from the thesis may be published without proper acknowledgement.

# Fabrication of Ultra-shallow Boron Junctions using Proximity Rapid Thermal Diffusion

by Martina Nolan

A thesis submitted for the degree of Doctor of Philosophy of the University of Dublin

Department of Electronic and Electrical Engineering University of Dublin, Trinity College, Ireland

### Declaration

I, the undersigned, declare that this thesis is entirely my own work, except where otherwise accredited, and that it has not been submitted for a degree at any other university or institution. I furthermore agree that the library may lend or copy this thesis upon request.

Signed,

Martina Nolan

30<sup>th</sup> of May 2000

### **Summary**

This work presents proximity rapid thermal diffusion (RTD) as a technique for fabricating shallow *p*-type junctions for LDD devices. Boron-doped spin-on dopant (SOD) is used as a dopant source in proximity RTD. Fourier transform infrared (FTIR) spectroscopy and spectroscopic ellipsometry are initially used to analyse and optimise the SOD dopant source.

Bare and oxidised silicon wafers are doped using the optimised SOD dopant source. The boron junctions are analysed using SIMS and the four-point probe technique. Boron diffusion coefficients are evaluated from the SIMS profiles using Boltzmann-Matano analysis.

Proximity RTD is used to fabricate p-n junction diodes. The diodes exhibit excellent current-voltage (IV) characteristics, with near ideal forward characteristics, low leakage currents and sharp avalanche breakdown voltages.

Micro-Raman spectroscopy (MRS), synchrotron X-ray topography (SXRT) and optical microscopy are used to determine the thermal stress and the boron-induced strain that is generated in wafers during rapid thermal oxidation (RTO) and rapid thermal diffusion. The thermal stress deteriorates with time at the peak temperature. The introduction of boron also generates extra strain in the lattice. However, the stress that is generated for very short process times is minimal and does not degrade device performance.

Finally, a LDD process that is compatible with proximity RTD is proposed.

### Acknowledgements

I would like to express my gratitude to several people who have helped to make this thesis possible.

Firstly, I would like to sincerely thank my supervisor, Dr. Alan Moore, for giving me the opportunity to undertake this research project and for his invaluable guidance and support. I would also like to thank Dr. Moore for encouraging me to participate in several stimulating international conferences.

I would like to thank Dr. Tania Perova for her endless encouragement and inspiration, and also for her assistance with FTIR analysis. Thanks also to Prof. J. Vij for use of his FTIR spectrometer.

This research project has involved collaborative work with numerous other groups. Above all, I would like to express my sincere gratitude to Prof. Harold Gamble, Queen's University Belfast, for his wonderful ideas and inspiring discussions, and also for providing me with access to all of the facilities in the Northern Ireland Semiconductor Research Centre (NISRC). I would also like to thank all of the friends that I have made in the NISRC for their hospitality and technical assistance, in particular, Dr. Paul Baine, Dr. Liam Quinn, Dr. S.H. Raza, Mr. Denis Campbell and Dr. John Montgomery for helping me to fabricate and test my *p-n* junction diodes.

Many thanks to Prof. John McGilp and Dr. Carlos Beitia, Physics Department, TCD, for their expertise in spectroscopic ellipsometry analysis and for many useful discussions. I would also like to thank Dr. Patrick McNally, Dublin City University, for giving me the opportunity to analyse my samples using synchrotron X-ray topography. Thanks also to Sean Hearne and Dr. Sverre Lidholm, National Microelectronics Research Centre, for their help with SIMS analysis.

Intel Ireland is gratefully acknowledged for their financial support of this research project. Thanks to Philip Moynagh, Dave Selkirk, Sarah McEvoy and Mike O'Connor in Intel for their assistance during the past few years, and in particular, thanks to my mentor Barry Kennedy for his advice and for the interest that he has shown in my work.

Special thanks to my friends Philippe Duval, Gerard Joyce, Vincent Ficet, Stephanie Kremer and Cormac Moore in the Fabrication Lab, TCD, for their support over the years.

Thanks to the staff of the Department of Electronic and Electrical Engineering for their encouragement and assistance.

I would like to thank my parents, Tom and Helen, for giving me the best of everything, including a wonderful education, and for supporting me in everything that I do. And last but not least, I would like to thank Richard Hunter for helping me in so many ways, and for always putting a smile on my face.

# Table of Contents

| Decl | aration  |          |                                               | ii   |

|------|----------|----------|-----------------------------------------------|------|

| Dedi | ication  |          |                                               | iii  |

| Sum  | mary     |          |                                               | iv   |

| Ackı | nowledg  | gements  |                                               | V    |

| Tabl | le of Co | ntents   |                                               | vii  |

| List | of Figu  | res      |                                               | xi   |

| List | of Tabl  | es       |                                               | xvi  |

| List | of Sym   | bols     |                                               | xvii |

| Acro | onyms a  | nd Abbi  | reviations                                    | xix  |

| Auth | or's Pu  | blicatio | ns                                            | xxi  |

| Pref | ace      |          |                                               | 1    |

| 1    | MOS      | Transis  | stor Device Physics                           | 3    |

|      | 1.1      | Introd   | uction                                        | 3    |

|      | 1.2      | MOS      | Capacitor                                     | 4    |

|      |          | 1.2.1    | Accumulation                                  | 5    |

|      |          | 1.2.2    | Depletion                                     | 5    |

|      |          | 1.2.3    | Inversion                                     | 5    |

|      |          | 1.2.4    | Strong Inversion                              | 5    |

|      | 1.3      | Long-    | Channel MOSFET                                | 6    |

|      |          | 1.3.1    | Subthreshold Currents in Long-Channel MOSFETs | 9    |

|      | 1.4      | Short-   | Channel MOSFET                                | 10   |

|      |          | 1.4.1    | Hot-Carrier Effects                           | 10   |

|      |          | 1.4.2    | Drain-induced-barrier-lowering (DIBL)         | 13   |

|      |          | 1.4.3    | Punchthrough                                  | 14   |

|      | 1.5      | Lightly  | y Doped Drain (LDD) Devices                   | 15   |

|      | 1.6      | Concli   | usions                                        | 18   |

| 2 | MOS                                         | SFET Doping Technology                                                 | 21 |  |

|---|---------------------------------------------|------------------------------------------------------------------------|----|--|

|   | 2.1                                         | Introduction                                                           | 21 |  |

|   | 2.2                                         | Ion Implantation                                                       | 21 |  |

|   | 2.3                                         | Rapid Thermal Diffusion                                                | 24 |  |

|   | 2.4                                         | Conclusions                                                            | 26 |  |

| 3 | Prox                                        | ximity Rapid Thermal Diffusion                                         | 29 |  |

|   | 3.1                                         | Introduction                                                           |    |  |

|   | 3.2                                         | Proximity Rapid Thermal Diffusion Process                              | 29 |  |

|   |                                             | 3.2.1 Experimental Procedure                                           | 31 |  |

|   | 3.3                                         | Removal of Contamination from Spin-on Dopants                          | 33 |  |

|   | 3.4                                         | Spin-on Dopants                                                        | 35 |  |

|   |                                             | 3.4.1 Spin-on Dopant B155                                              | 35 |  |

|   |                                             | 3.4.2 Spin-on Dopant B153                                              | 36 |  |

|   | 3.5                                         | B153 Doping Effectiveness                                              | 37 |  |

|   | 3.6                                         | Conclusions                                                            | 40 |  |

| 4 | Stabilisation of B153 Spin-on Dopant Source |                                                                        |    |  |

|   | 4.1                                         | Introduction                                                           | 42 |  |

|   | 4.2                                         | Experimental Procedure                                                 | 43 |  |

|   |                                             | 4.2.1 Proximity Rapid Thermal Diffusion                                | 43 |  |

|   |                                             | 4.2.2 FTIR Measurements                                                | 44 |  |

|   |                                             | 4.2.3 Spectroscopic Ellipsometry Measurements                          | 45 |  |

|   |                                             | 4.2.4 SIMS and Sheet Resistance Measurements                           | 45 |  |

|   | 4.3                                         | Results and Discussion                                                 | 46 |  |

|   |                                             | 4.3.1 FTIR                                                             | 46 |  |

|   |                                             | 4.3.2 Spectroscopic Ellipsometry                                       | 50 |  |

|   | 4.4                                         | B <sub>2</sub> O <sub>3</sub> Transfer to the Product Wafer            | 55 |  |

|   |                                             | 4.4.1 B <sub>2</sub> O <sub>3</sub> Step Coverage on the Product Wafer | 55 |  |

|   |                                             | 4.4.2 B <sub>2</sub> O <sub>3</sub> Layer Removal                      | 55 |  |

|   | 4.5                                         | Conclusions                                                            | 55 |  |

| 5 | Boro                                               | n Diffus | sion & Properties of Proximity RTD Doped Wafers            | 60  |  |

|---|----------------------------------------------------|----------|------------------------------------------------------------|-----|--|

|   | 5.1                                                | Introd   | uction                                                     | 60  |  |

|   | 5.2                                                | Boron    | Diffusion                                                  | 61  |  |

|   |                                                    | 5.2.1    | Diffusion Mechanisms                                       | 61  |  |

|   |                                                    | 5.2.2    | Fractional Interstitialcy Component                        | 63  |  |

|   |                                                    | 5.2.3    | Oxidation-Enhanced Diffusion                               | 64  |  |

|   |                                                    | 5.2.4    | Transient-Enhanced Diffusion                               | 65  |  |

|   |                                                    | 5.2.5    | Other Anomalous Diffusion Effects                          | 66  |  |

|   | 5.3                                                | Enhan    | nced Diffusion of Boron from Borosilicate Glass during RTD | 66  |  |

|   | 5.4                                                | Proper   | rties of Proximity RTD Doped Product Wafers                | 67  |  |

|   |                                                    | 5.4.1    | Sheet Resistance Measurements and SIMS Analysis            | 67  |  |

|   |                                                    | 5.4.2    | Diffusion Coefficients                                     | 71  |  |

|   |                                                    | 5.4.3    | Comparison with other Fabrication Techniques               | 74  |  |

|   | 5.5                                                | Concl    | usions                                                     | 75  |  |

| 6 | Electrical Characterisation of p-n Junction Diodes |          |                                                            |     |  |

|   | 6.1                                                | Introd   | luction                                                    | 78  |  |

|   | 6.2                                                | Fabric   | eation of <i>p-n</i> Junction Diodes                       | 79  |  |

|   | 6.3                                                | The Id   | deal Diode Equation                                        | 81  |  |

|   | 6.4                                                | Forwa    | ard IV Characteristics                                     | 83  |  |

|   |                                                    | 6.4.1    | Surround Diodes (SD)                                       | 83  |  |

|   |                                                    | 6.4.2    | Open Diodes Type 1 (OD1)                                   | 87  |  |

|   |                                                    | 6.4.3    | Open Diodes Type 2 (OD2)                                   | 88  |  |

|   |                                                    | 6.4.4    | High Level Injection and Series Resistance                 | 89  |  |

|   | 6.5                                                | Rever    | se IV Characteristics                                      | 91  |  |

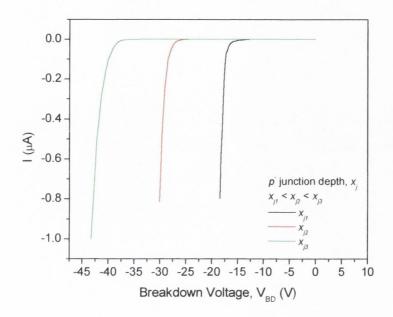

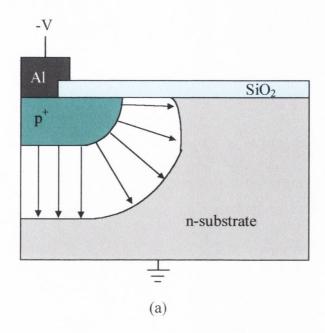

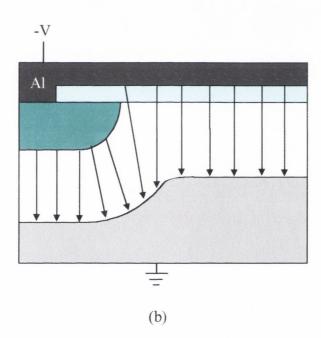

|   |                                                    | 6.5.1    | Influence of Junction Curvature on Breakdown Voltage       | 91  |  |

|   |                                                    | 6.5.2    | Open Diodes Type 2 (OD2)                                   | 94  |  |

|   |                                                    | 6.5.3    | Surround Diodes (SD)                                       | 97  |  |

|   |                                                    | 6.5.4    | Open Diodes Type 1 (OD1)                                   | 99  |  |

|   | 6.6                                                | Concl    | usions                                                     | 100 |  |

|   |                                                    |          |                                                            |     |  |

| 7    | Stres                                     | s Generated in Silicon during Rapid Thermal Processing     | 102 |  |

|------|-------------------------------------------|------------------------------------------------------------|-----|--|

|      | 7.1                                       | Introduction                                               | 102 |  |

|      | 7.2                                       | Micro-Raman Spectroscopy (MRS)                             | 103 |  |

|      |                                           | 7.2.1 Experimental Procedure                               | 104 |  |

|      |                                           | 7.2.2 Extracting Information from Raman Spectra            | 104 |  |

|      | 7.3                                       | Synchrotron X-Ray Topography (SXRT)                        | 105 |  |

|      |                                           | 7.3.1 Experimental Procedure                               | 106 |  |

|      | 7.4                                       | Stress Generated during Proximity Rapid Thermal Processing | 107 |  |

|      |                                           | 7.4.1 Thermal Stress                                       | 108 |  |

|      |                                           | 7.4.2 Boron-Induced Strain                                 | 111 |  |

|      | 7.5                                       | Conclusions                                                | 114 |  |

| 8    | LDD and Proximity RTD Process Integration |                                                            |     |  |

|      | 8.1                                       | Introduction                                               | 116 |  |

|      | 8.2                                       | Conventional LDD Device Fabrication                        | 116 |  |

|      | 8.3                                       | Limitations of Conventional LDD Devices                    |     |  |

|      | 8.4                                       | Improvements to the Conventional LDD Structure and         |     |  |

|      |                                           | Proposed Integration of Proximity RTD                      |     |  |

|      | 8.5                                       | Conclusions                                                | 124 |  |

| 9    | Conc                                      | lusions and Suggestions for Future Work                    | 126 |  |

|      | 9.1                                       | Conclusions                                                | 126 |  |

|      | 9.2                                       | Future Work                                                | 128 |  |

| Appe | ndix                                      |                                                            |     |  |

| A    | Masl                                      | Set for p-n Junction Diodes                                | 130 |  |

| В    | Proc                                      | ess Flow for p-n Junction Diodes                           | 134 |  |

# List of Figures

| 1.1  | (a) Perspective view of a MOS-C, (b) Cross-section of a MOS-C.                               | 4  |

|------|----------------------------------------------------------------------------------------------|----|

| 1.2  | (a) Perspective view of a MOSFET, (b) Cross-section of a MOSFET.                             | 6  |

| 1.3  | (a) $I_D$ - $V_{DS}$ characteristic of a MOSFET being operated at a fixed $V_{GS}$ > $V_T$ ; |    |

|      | (b) $V_{DS}=0$ V; (c) inversion layer narrowing under moderate $V_{DS}$ biasing;             |    |

|      | (d) pinch-off, $V_{DS}=V_{SSAT}$ ; and (e) post pinch-off, $V_{DS}>V_{DSSAT}$ .              | 8  |

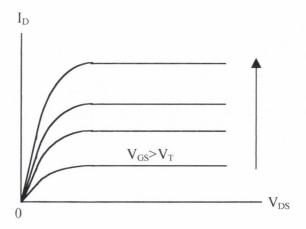

| 1.4  | I <sub>D</sub> -V <sub>DS</sub> characteristic for a long-channel MOSFET.                    | 9  |

| 1.5  | Cross-section of a PMOS transistor showing hot-carrier processes.                            | 11 |

| 1.6  | Hot electron injection into the gate oxide in a PMOS transistor.                             | 12 |

| 1.7  | (a) Reverse biased pn junction; (b) Cross-section of a PMOS transistor                       |    |

|      | showing electric field lines from the channel charge terminating on                          |    |

|      | acceptor ions in the source and drain depletion regions.                                     | 13 |

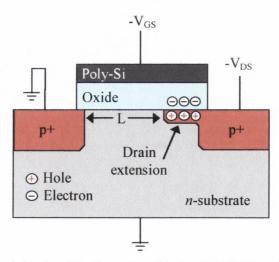

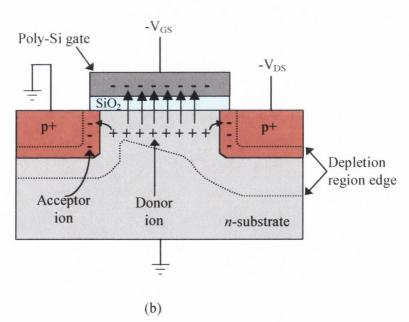

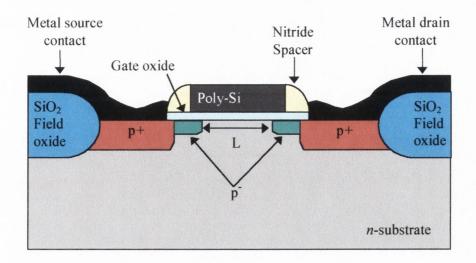

| 1.8  | Cross-section of a LDD PMOS transistor.                                                      | 15 |

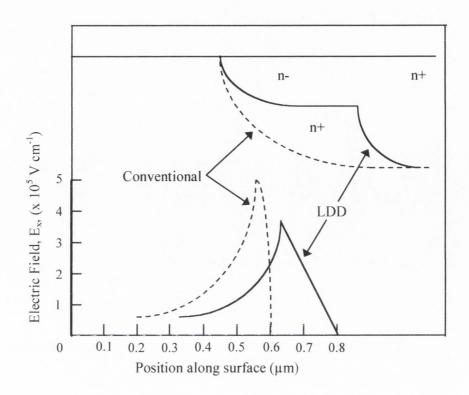

| 1.9  | Magnitude of the electric field at the Si-SiO <sub>2</sub> interface as a function of        |    |

|      | distance: L = 1.2 $\mu$ m, V <sub>DS</sub> = 8.5 V, V <sub>GS</sub> = V <sub>T</sub> [2]     | 16 |

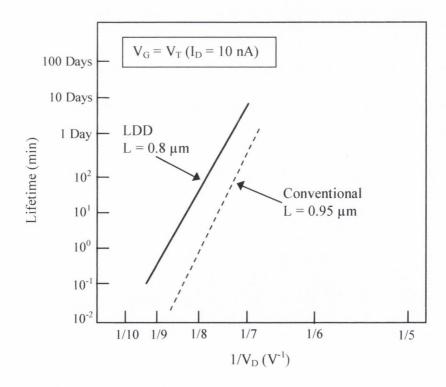

| 1.10 | Device lifetime versus reciprocal stressing drain voltage for a                              |    |

|      | conventional PMOSFET and a LDD PMOSFET [1].                                                  | 16 |

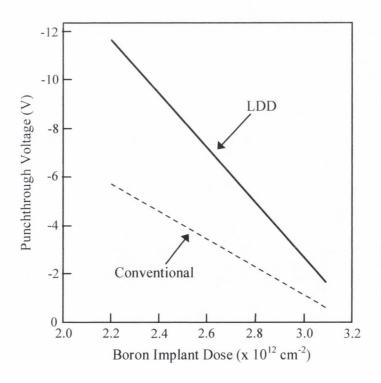

| 1.11 | Punchthrough voltage as a function of boron implant dose for a $0.4\ \mu m$                  |    |

|      | PMOSFET with and without an LDD structure [3].                                               | 17 |

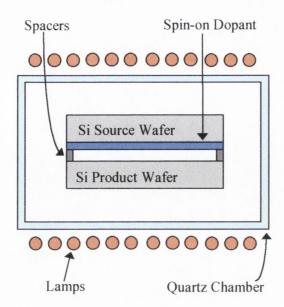

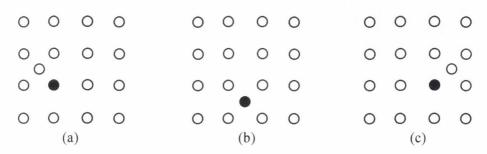

| 3.1  | Wafer Configuration in Proximity RTD.                                                        | 30 |

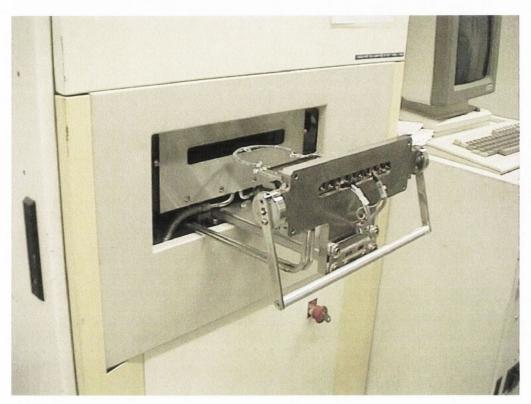

| 3.2  | Sitesa rapid thermal processor.                                                              | 31 |

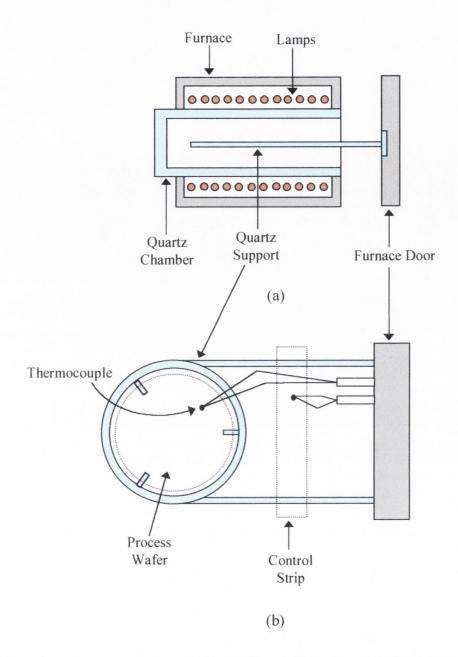

| 3.3  | Schematic representation of Sitesa RTP. a) Side-view of RTP; b) Plan-                        |    |

|      | view of the quartz support.                                                                  | 32 |

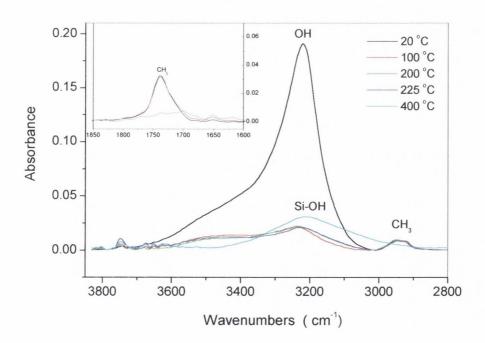

| 3.4  | FTIR spectra of the source wafers after 15 minutes at various post-spin                      |    |

|      | baking temperatures.                                                                         | 34 |

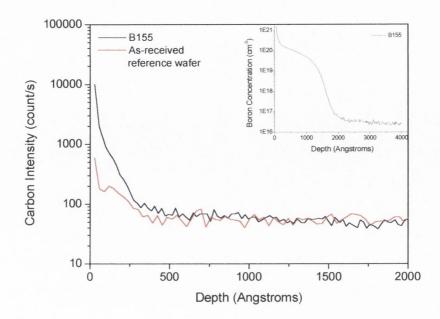

| 3.5  | SIMS Carbon and Boron profiles of a product wafer that was doped with                        |    |

|      | B155 during a RTD at 1050 °C for 16 s.                                                       | 35 |

|      |                                                                                              |    |

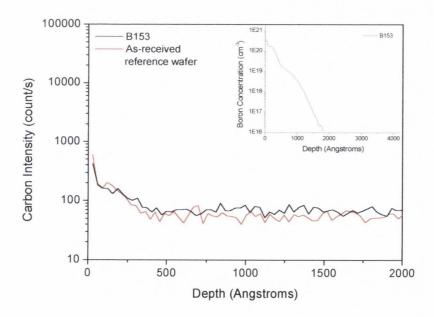

| 3.6  | SIMS Boron and Carbon profiles of a product wafer that was doped using   |    |

|------|--------------------------------------------------------------------------|----|

|      | B153 in RTD 1050 °C for 16 s.                                            | 36 |

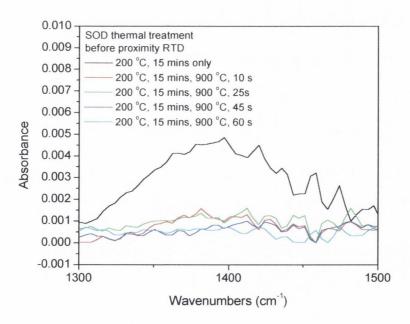

| 3.7  | FTIR spectra of product wafers that were doped at 1050 °C for 16 s. Each |    |

|      | SOD source received a different thermal treatment prior to diffusion.    | 38 |

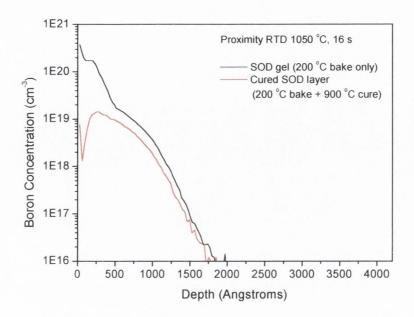

| 3.8  | SIMS profiles of junctions that were formed by diffusion of boron from a |    |

|      | SOD gel and a cured SOD layer.                                           | 39 |

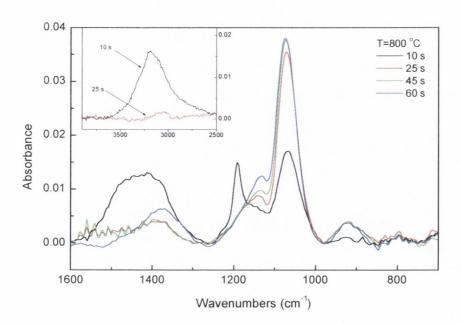

| 4.1  | IR absorbance spectra of SOD layers which were annealed at 800 °C for    |    |

|      | various times.                                                           | 46 |

| 4.2  | IR absorbance spectra of SOD layers which were annealed at 900 °C for    |    |

|      | various times.                                                           | 47 |

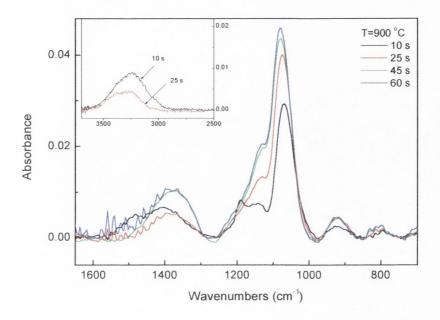

| 4.3  | IR absorbance spectra of SOD layers which were annealed at 1000 °C for   |    |

|      | various times.                                                           | 47 |

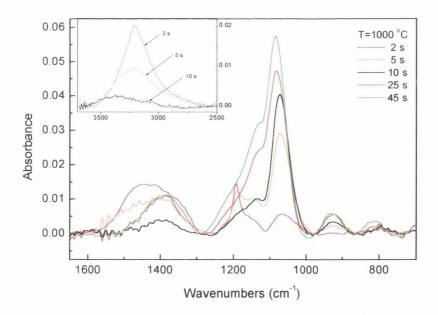

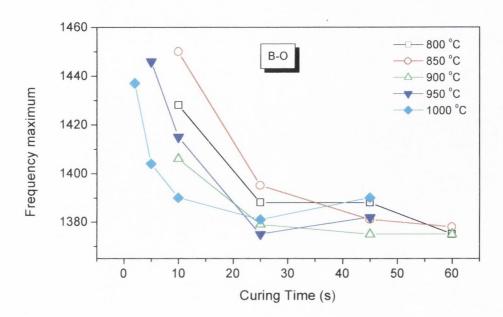

| 4.4  | The dependence of the peak intensity of Si-O-Si stretching vibrations    |    |

|      | band on RTC temperature and time.                                        | 48 |

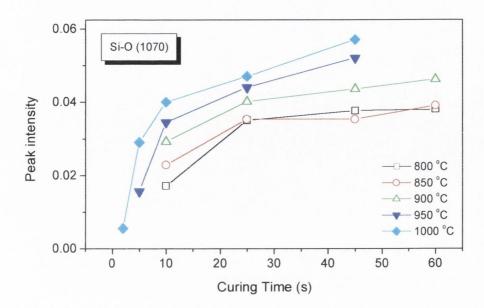

| 4.5  | The dependence of the peak position of B-O stretching vibrations band on |    |

|      | RTC temperature and time.                                                | 49 |

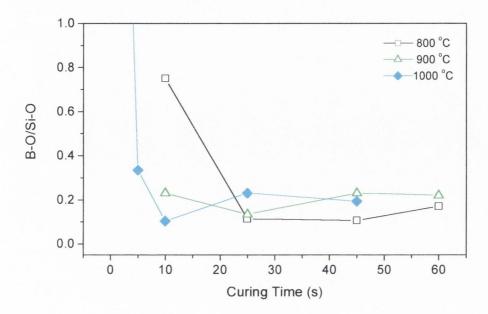

| 4.6  | The dependence of the B-O/Si-O infrared peak ratio on curing time for    |    |

|      | different temperatures.                                                  | 50 |

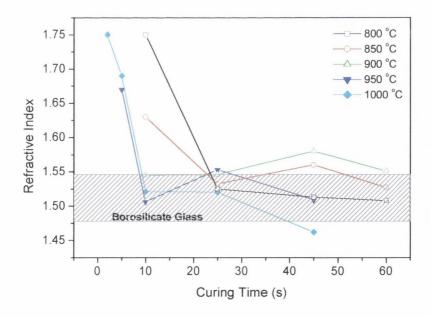

| 4.7  | The dependence of the refractive index of SOD layers on RTA              |    |

|      | temperature and time.                                                    | 51 |

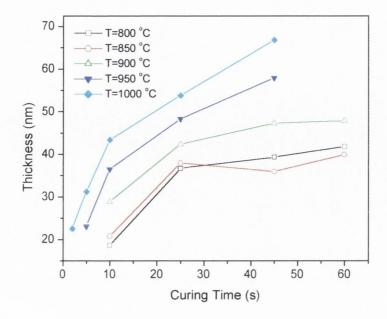

| 4.8  | Variation in thickness of SOD layers (ellipsometry measurements) with    |    |

|      | changing RTA temperature and time.                                       | 53 |

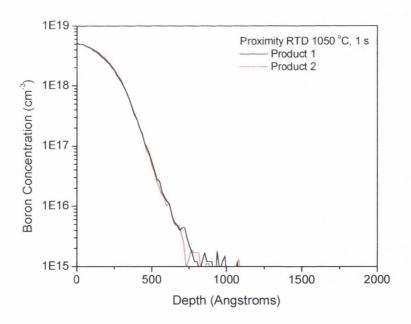

| 4.9  | SIMS B concentration profiles of two silicon wafers that were doped by a |    |

|      | single dopant source in proximity RTD.                                   | 54 |

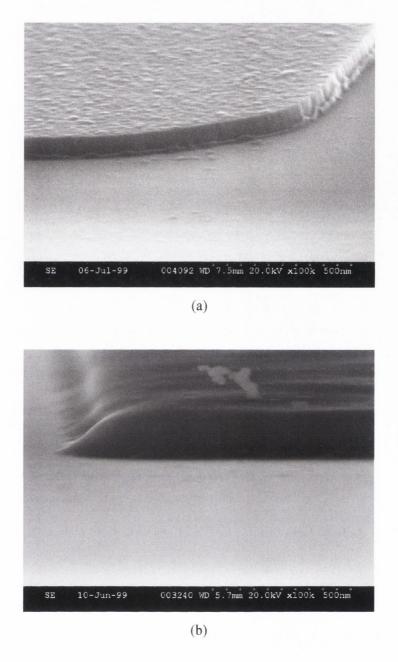

| 4.10 | SEM micrographs (x100k) (a) Plasma-etched polysilicon gate structure;    |    |

|      | (b) Polysilicon gate covered in a conformal B2O3 layer after proximity   |    |

|      | RTD.                                                                     | 56 |

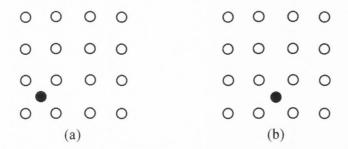

| 5.1  | Diffusion by the interstitial mechanism.                                 | 62 |

| 5.2  | Diffusion by the substitutional mechanism.                               | 62 |

| 5.3  | Interstitial-substitutional diffusion by the dissociative mechanism.     | 62 |

| 5.4  | Interstitial-substitutional diffusion by the kick-out mechanism.         | 62 |

| 5.5  | Interstitialcy diffusion process.                                        | 62 |

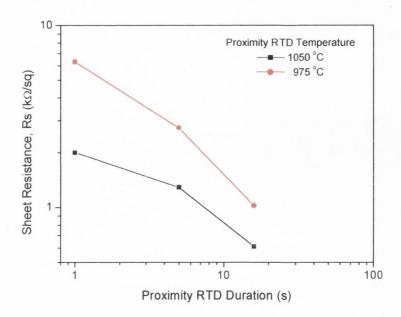

| 5.6  | Sheet resistance of doped product wafers as a function of RTD duration at                       |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | 975 °C and 1050 °C.                                                                             | 67 |

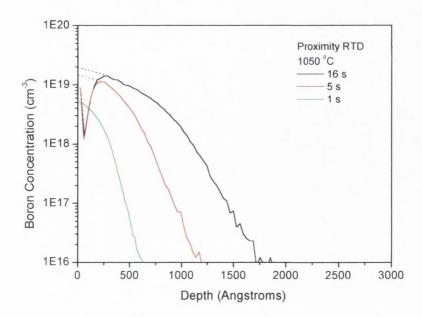

| 5.7  | Boron concentration profiles of bare silicon wafers that were doped                             |    |

|      | during proximity RTD at 1050 °C for various durations.                                          | 68 |

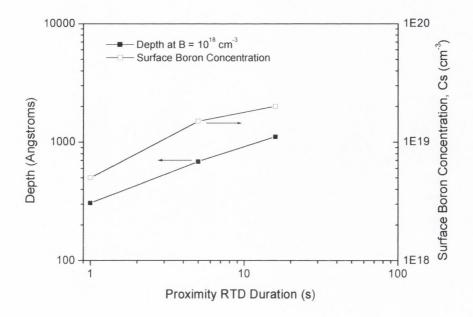

| 5.8  | Surface boron concentration and junction depth as a function of RTD                             |    |

|      | duration.                                                                                       | 69 |

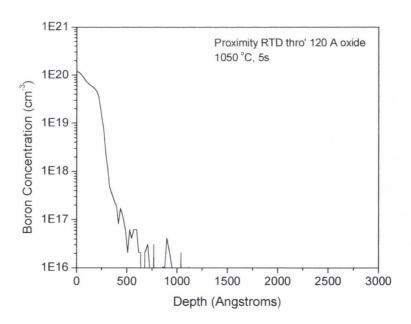

| 5.9  | SIMS concentration profile of an oxidised wafer that was doped wafer                            |    |

|      | during proximity RTD at 1050 °C for 5 s.                                                        | 70 |

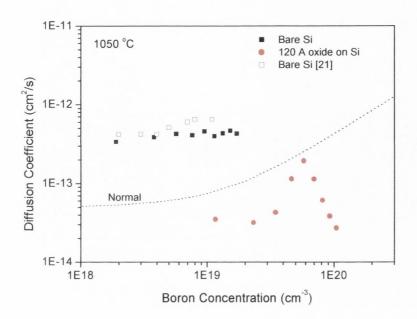

| 5.10 | Dependence of boron diffusion coefficient on boron concentration in Si,                         |    |

|      | evaluated from 16 s proximity RTD into bare Si at 1050 °C, and from a                           |    |

|      | 5 s RTD through a 120 Å oxide on Si at 1050 °C. The dotted curve                                |    |

|      | represents the normal diffusion coefficient.                                                    | 72 |

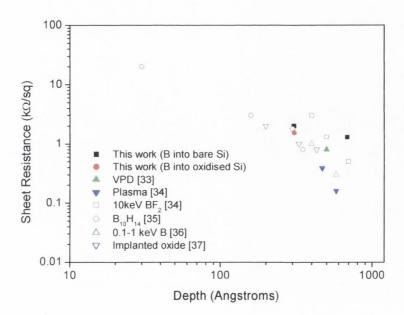

| 5.11 | Junction depth at 10 <sup>18</sup> cm <sup>-3</sup> versus sheet resistance for various shallow |    |

|      | boron junction formation techniques.                                                            | 74 |

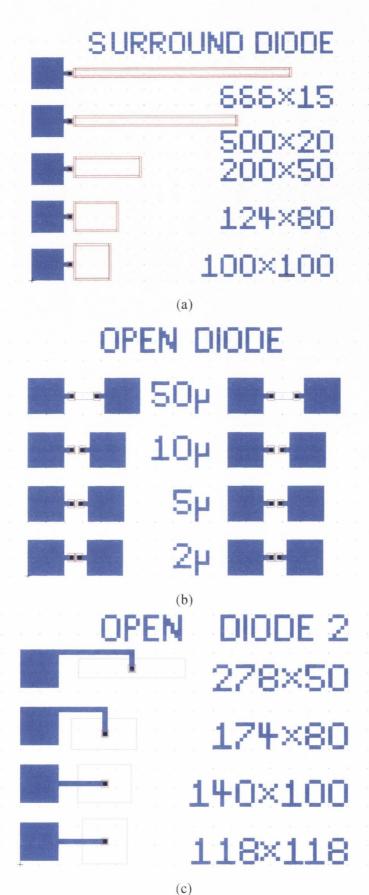

| 6.1  | Mask Layout for Surround Diodes (SD), Open Diodes type 1 (OD1), and                             |    |

|      | Open Diodes type 2 (OD2).                                                                       | 80 |

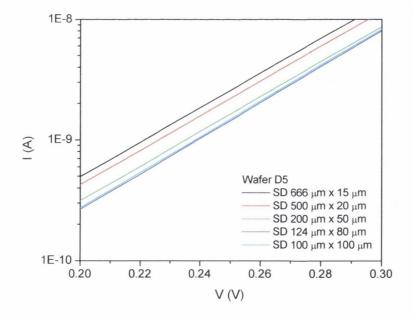

| 6.2  | Forward IV characteristics of surround diodes on wafer D5.                                      | 84 |

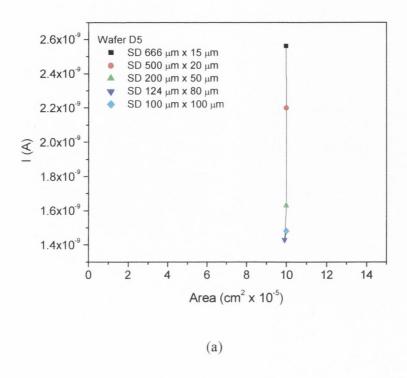

| 6.3  | Current v's the total p-type area of surround diodes on (a) wafer D5 and                        |    |

|      | (b) wafer D4.                                                                                   | 85 |

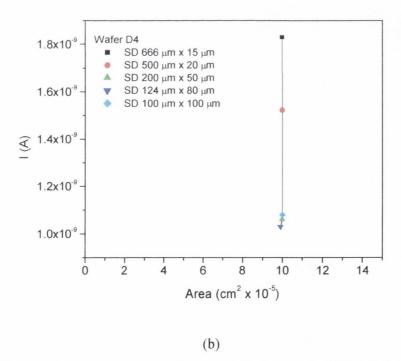

| 6.4  | (a) Current crowding in a surround diode, (b) As width x increases, the                         |    |

|      | current crowding increases in the diode.                                                        | 86 |

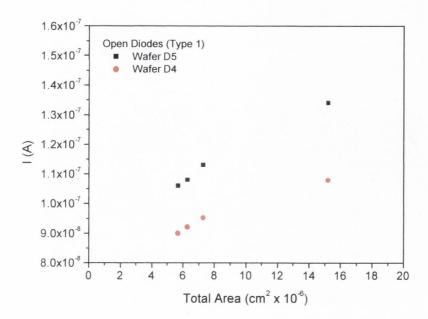

| 6.5  | Current v's total area of OD1 diodes in wafers D4 and D5.                                       | 88 |

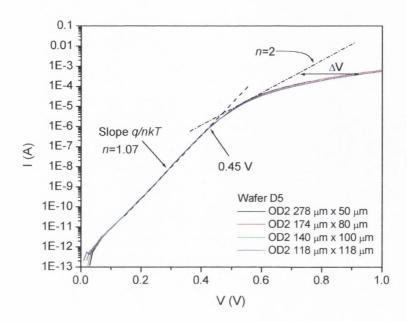

| 6.6  | Forward bias IV characteristics for OD2 diodes on wafer D5.                                     | 89 |

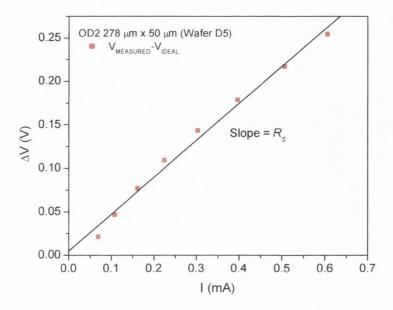

| 6.7  | $\Delta V$ versus I for OD2 278 $\mu$ m x 50 $\mu$ m. The slope of the graph is the             |    |

|      | series resistance, R <sub>s</sub> , of the diode.                                               | 91 |

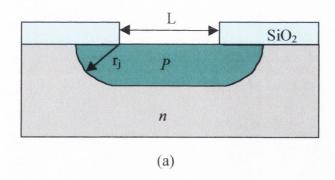

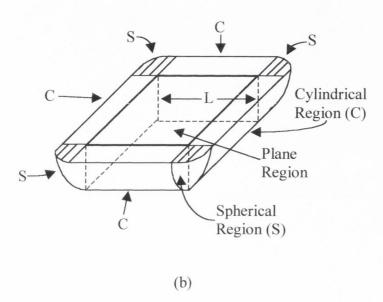

| 6.8  | (a) Planar diffusion process that forms junction curvature near the edge of                     |    |

|      | the diffusion mask, where $r_j$ is the radius of curvature. (b) Formation of                    |    |

|      | the cylindrical and spherical regions by diffusion through a rectangular                        |    |

|      | mask.                                                                                           | 92 |

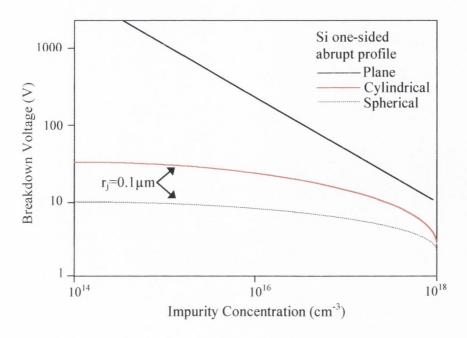

| 6.9  | Breakdown voltage versus impurity concentration for one-sided abrupt                            |    |

|      | doping profile with cylindrical and spherical junction geometries, where                        |    |

|      | rj is the radius of curvature as indicated in Fig. 6.14 [2].                                    | 93 |

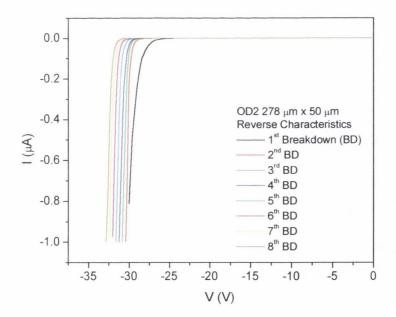

| 6.10 | Breakdown voltages of OD2 278 μm x 50 μm.                                                                                     | 93  |

|------|-------------------------------------------------------------------------------------------------------------------------------|-----|

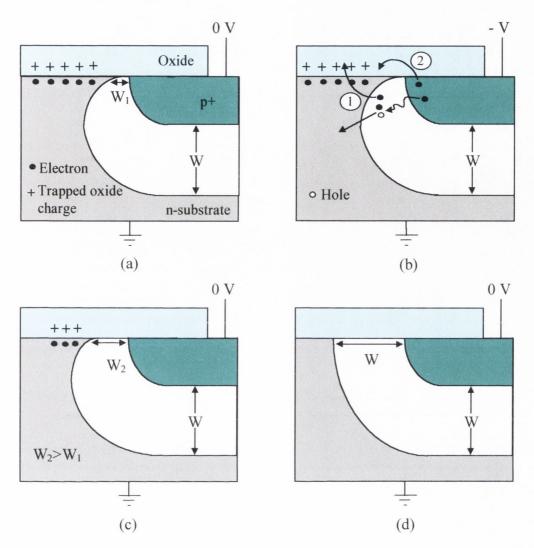

| 6.11 | (a) Accumulation of electrons at the oxide-substrate interface reduces                                                        |     |

|      | depletion width to W <sub>1</sub> , W <sub>1</sub> < <w (b)="" avalanche="" multiplication="" process<="" td=""><td></td></w> |     |

|      | injects an electron into the oxide (c) Injected electron causes depletion                                                     |     |

|      | width to change to W2, W2>W1 (d) If avalanche breakdown is repeated,                                                          |     |

|      | depletion width at oxide-substrate interface increases an saturates to W.                                                     | 95  |

| 6.12 | Breakdown voltages for OD2 278 μm x 50 μm on wafer D5.                                                                        | 97  |

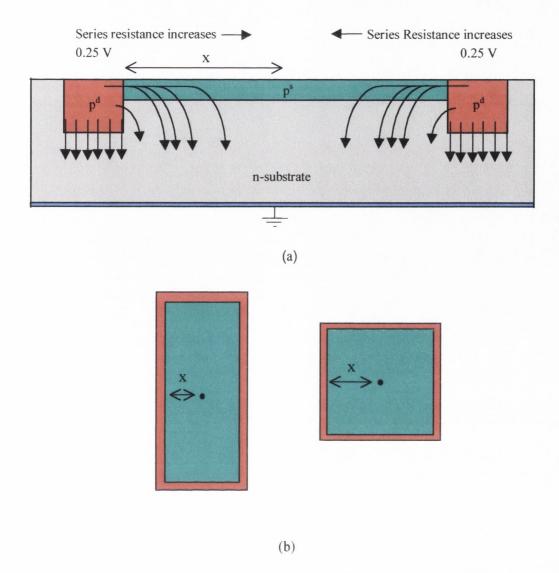

| 6.13 | Shape of the depletion region around (a) SD 666 x 15 $\mu m$ and (b) SD 100 x 100 $\mu m$ .                                   | 98  |

| 6.14 | Influence of field-plate voltage on the shape of the depletion region. (a)                                                    |     |

|      | p- $n$ junction with no field-plate (b) $p$ - $n$ junction with a field-plate.                                                | 100 |

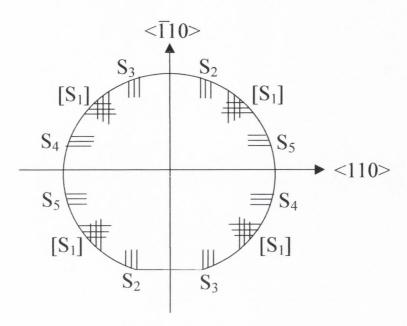

| 7.1  | Locations of the maxima of the thermally induced resolved stresses and                                                        |     |

|      | the corresponding slip line directions on a <100> silicon wafer.                                                              | 103 |

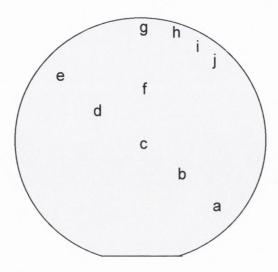

| 7.2  | Raman spectra were measured at points a-j across each wafer.                                                                  | 105 |

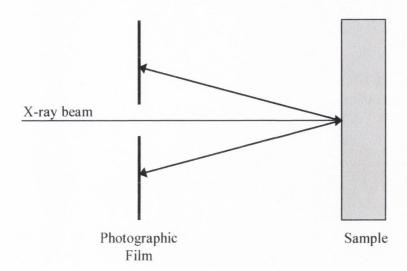

| 7.3  | Schematic diagram of White Light Back Reflection Topography.                                                                  | 107 |

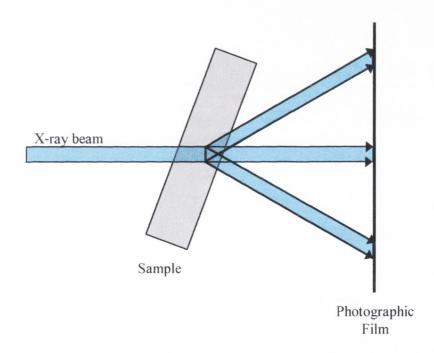

| 7.4  | Schematic diagram of White Beam Topography in Section Topography                                                              |     |

|      | Mode.                                                                                                                         | 107 |

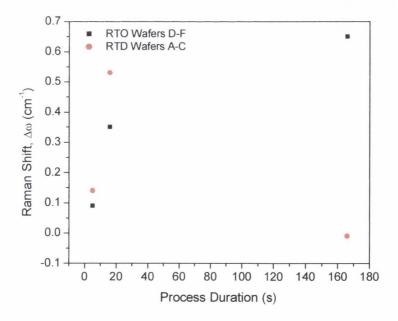

| 7.5  | Raman shift, $\Delta\omega$ , as a function of process duration for RTO and RTD at                                            |     |

|      | 1050 °C.                                                                                                                      | 109 |

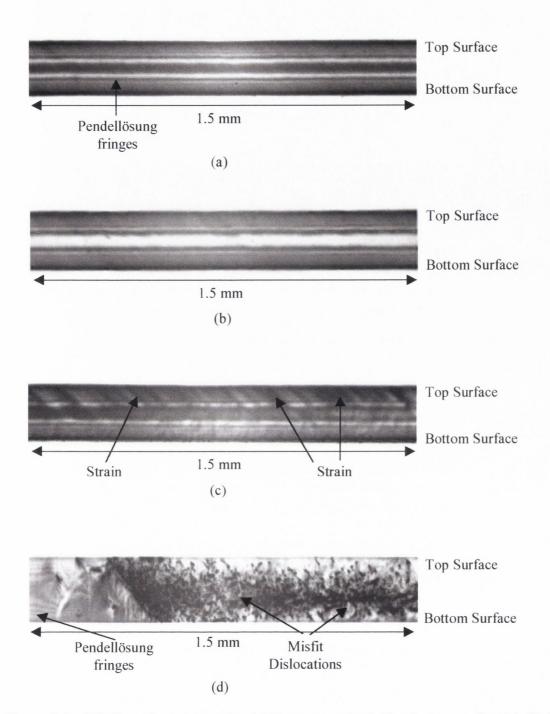

| 7.6  | SXRT section topographs: (a) Bare as-received Si reference wafer; (b)                                                         |     |

|      | Wafer F: RTO for 166 s at 1050 °C; (c) Wafer A: RTD for 5 s at 1050 °C;                                                       |     |

|      | (d) Wafer C: RTD for 166 s at 1050 °C.                                                                                        | 112 |

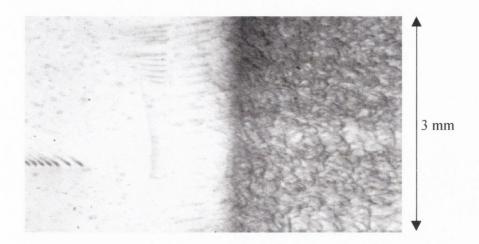

| 7.7  | SXRT back reflection topograph of wafer F.                                                                                    | 113 |

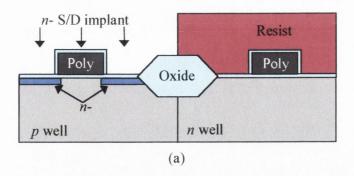

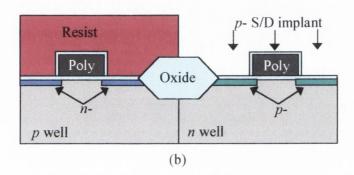

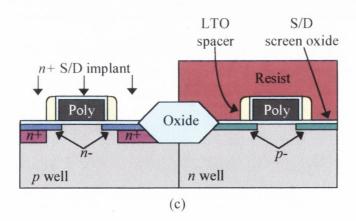

| 8.1  | Conventional LDD spacer process. (a) Selective n- implantation; (b)                                                           |     |

|      | Selective p- implantation; (c) LTO spacer deposition and RIE, followed                                                        |     |

|      | by a source/drain screen oxidation. Next, a selective n+ implantation is                                                      |     |

|      | performed; (d) Selective p+ implantation.                                                                                     | 117 |

| 8.2  | Drain current in conventional and LDD MOSFETs [6].                                                                            | 119 |

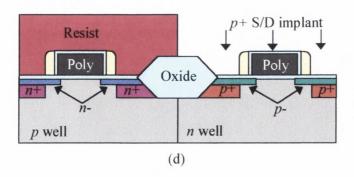

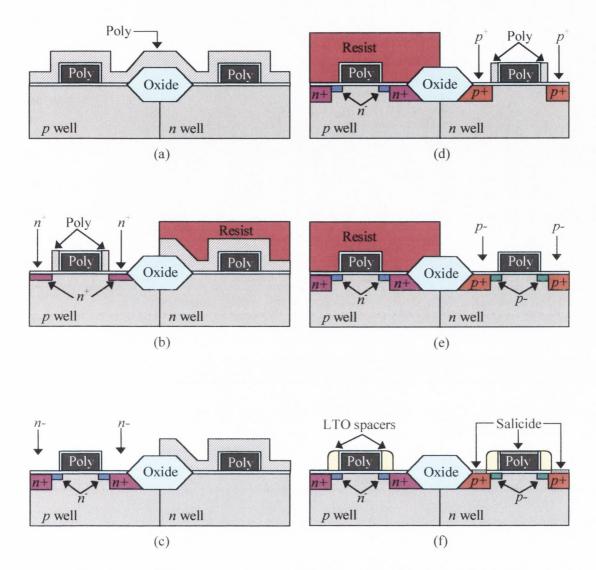

| 8.3 | Disposable spacer process. (a) Undoped polysilicon is deposited as the    |     |

|-----|---------------------------------------------------------------------------|-----|

|     | spacer material. (b) Using resist to cover PMOS areas, the NMOS is        |     |

|     | formed and followed by an arsenic n+ implantation. The resist is stripped |     |

|     | and the arsenic profile is annealed. (c) A blanket phosphorus n- implant  |     |

|     | is performed which uses the non-etched polysilicon spacer material to     |     |

|     | protect the PMOS areas. (d) Using the second patterning step, the NMOS    |     |

|     | areas are covered with resist and the PMOS poly spacers are formed,       |     |

|     | followed by the p+ source/drain implant. (e) The spacers are removed      |     |

|     | and the p- implant is performed. (f) The resist is stripped and the       |     |

|     | permanent LTO spacers are formed to define the salicided                  |     |

|     | source/drain/gate regions. Conventional processing follows with contact   |     |

|     | and aluminium metallisation definition. [1].                              | 121 |

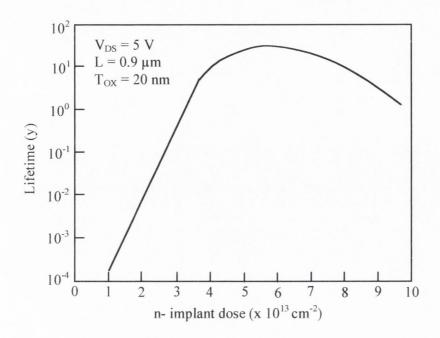

| 8.4 | The dependence of device lifetime on the LDD n- implant dose. The         |     |

|     | maximum lifetime point is at $5-6\times10^{13}$ cm <sup>-2</sup> [10].    | 123 |

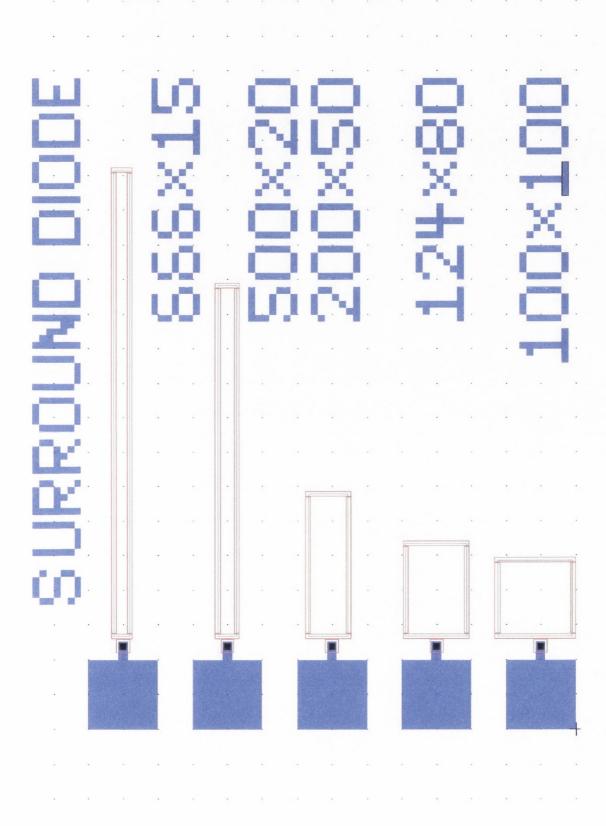

| A.1 | Mask set for Surround Diodes.                                             | 131 |

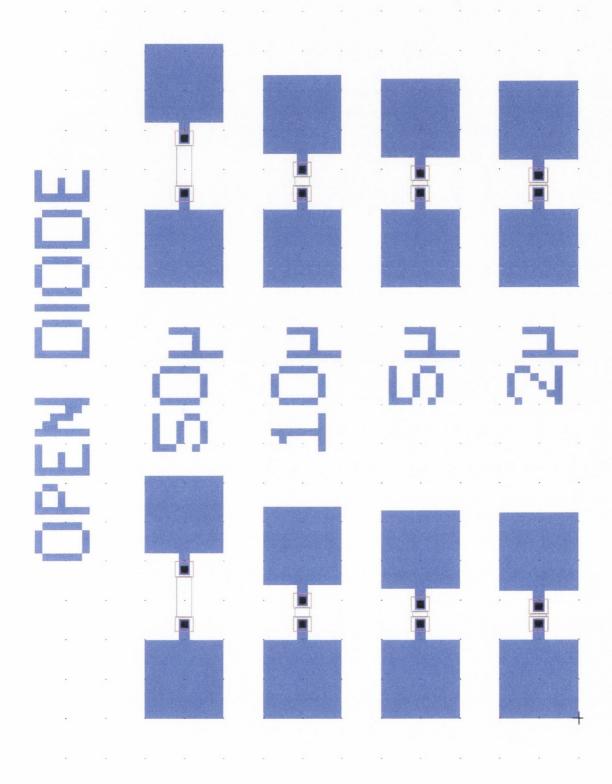

| A.2 | Mask set for Open Diodes type 1.                                          | 132 |

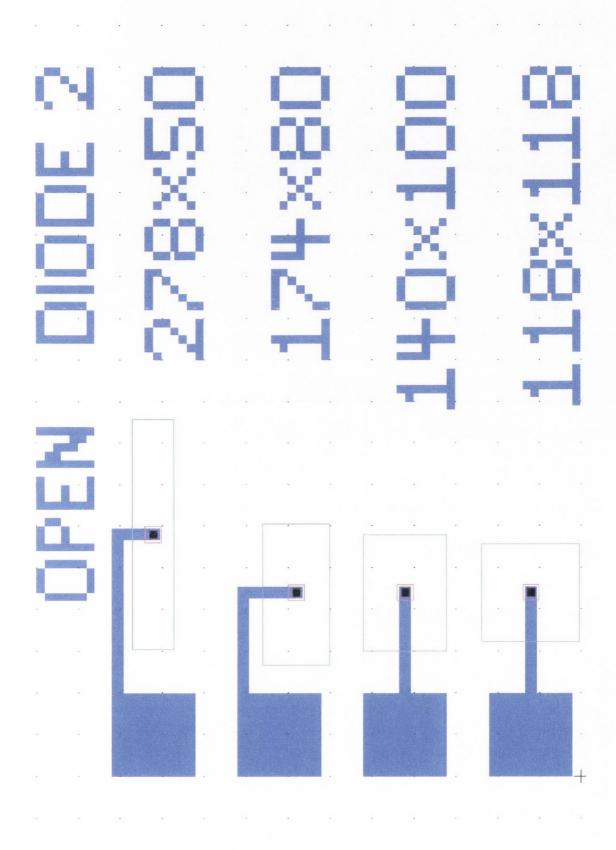

| A.3 | Mask set for Open Diodes type 2.                                          | 133 |

## List of Tables

| 1.1 | Projected LDD junction depths versus gate lengths [4].                   | 18  |

|-----|--------------------------------------------------------------------------|-----|

| 3.1 | Sheet resistance of 3 wafers that were doped with a single dopant source |     |

|     | wafer.                                                                   | 37  |

| 4.1 | Rapid thermal treatment to convert SOD gel to BSG.                       | 44  |

| 6.1 | Ideality factor, $n$ , and $I_0$ for wafers D5 and D4.                   | 84  |

| 7.1 | Rapid thermally processed samples.                                       | 108 |

| 7.2 | Measured Raman peak shift, $\Delta\omega$ , for oxidised wafers D-F.     | 109 |

| 7.3 | Measured Raman peak shift, $\Delta\omega$ , for doped wafers A-C.        | 110 |

| 7.4 | Measured Raman half widths, $\Gamma$ , for wafers F, A and C.            | 113 |

# List of Symbols

| A         | Cross-sectional area (cm <sup>2</sup> )                                |

|-----------|------------------------------------------------------------------------|

| $A_J$     | Junction area (cm <sup>2</sup> )                                       |

| $A_S$     | Area of the depletion region at the silicon surface (cm <sup>2</sup> ) |

| B         | Body/substrate                                                         |

| $C_s$     | Surface concentration (cm <sup>-3</sup> )                              |

| D         | Drain                                                                  |

| $D_i$     | Intrinsic diffusion coefficient (cm <sup>2</sup> /s)                   |

| $D_P$     | Hole diffusion constant (cm <sup>2</sup> /s)                           |

| $E_Y$     | Horizontal electric field (V/cm)                                       |

| $f_{AI}$  | Fractional interstitialcy component                                    |

| $g_m$     | Transconductance (A/V)                                                 |

| G         | Gate                                                                   |

| I         | Current (A)                                                            |

| $I_D$     | Drain current (A)                                                      |

| $I_{DST}$ | Subthreshold current (A)                                               |

| $I_{GEN}$ | Generation current (A)                                                 |

| $I_{REC}$ | Recombination current (A)                                              |

| k         | Boltzmann's constant (8.62 x 10 <sup>-5</sup> eV/°K)                   |

| L         | Channel length                                                         |

| n         | Ideality factor                                                        |

| $n_i$     | Intrinsic carrier concentration (cm <sup>-3</sup> )                    |

| $N_D$     | Donor impurity concentration (cm <sup>-3</sup> )                       |

| q         | Charge on an electron (1.602 x 10 <sup>-19</sup> C)                    |

| $R_s$     | Sheet resistance ( $\Omega$ /sq)                                       |

| S         | Source                                                                 |

| $S_0$     | Surface recombination velocity (cm/s)                                  |

| T         | Tomporatura                                                            |

$V_A$  Applied voltage (V)

$V_{DB}$  Drain-body voltage (V)

$V_{DS}$  Drain-source voltage (V)

$V_{DSSAT}$  Pinch-off voltage (V)

$V_{GB}$  Gate-body voltage (V)

$V_{GS}$  Gate-source voltage (V)

$V_{SB}$  Source-body voltage (V)

$V_T$  Threshold voltage (V)

$x_j$  Junction Depth

$\Delta\omega$  Raman shift (cm<sup>-1</sup>)

ε Misfit factor

$\Gamma$  Raman half width (cm<sup>-1</sup>)

σ Stress (Pa)

$\tau_g$  Generation lifetime (s)

$\tau_0$  Effective lifetime of carriers in the depletion region (s)

$\tau_P$  Hole minority carrier lifetime (s)

### Acronyms and Abbreviations

APCVD Atmospheric Pressure Chemical Vapour Deposition

BPSG Borophosphosilicate Glass

BRT Back Reflection Topography

BSG Borosilicate Glass

DIBL Drain Induced Barrier Lowering

FD Furnace Diffusion

FTIR Fourier Transform Infrared Spectroscopy

GILD Gas Immersion Laser Doping

GOLD Gate-drain Overlapped LDD

IC Integrated Circuit

IR Infrared

ITLDD Inverse-T Lightly Doped Drain

LDD Lightly Doped Drain

LOCOS Local Oxidation of Silicon

LPCVD Low Pressure Chemical Vapour Deposition

LTO Low Temperature Oxide

MLDD Moderate Lightly Doped Drain

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MRS Micro Raman Spectroscopy

OD1 Open Diode type 1

OD2 Open Diode type 2

OED Oxidation Enhanced Diffusion

PSG Phosphosilicate Glass

RIE Reactive Ion Etching

RTC Rapid Thermal Cure

RTD Rapid Thermal Diffusion

RTO Rapid Thermal Oxidation

#### Acronyms and Abbreviations

RTP Rapid Thermal Processor

RVD Rapid Vapour-phase Diffusion

SD Surround Diode

SEM Scanning Electron Microscope

SIA Semiconductor Industry Association

SIMS Secondary Ion Mass Spectrometry

SOD Spin On Dopant

SOG Spin On Glass

SOI Silicon On Insulator

ST Section Topography

SUPREM Stanford University Process Engineering Model

SXRT Synchrotron X-ray Topography

TED Transient Enhanced Diffusion

TEOS Tetraethylorthosilane

TOPS Total Overlap with Polysilicon Spacer

ULSI Ultra Large Scale Integration

VLSI Very Large Scale Integration

### **Author's Publications**

#### Refereed Journal Publications

- M. Nolan, T. Perova, R.A. Moore and H.S. Gamble, "Boron diffusion from a spin-on source during rapid thermal processing", *J. Non-Crystalline Solids*, 254, 89-93, (1999).

- 2. **M. Nolan**, T. Perova, R.A. Moore, C.J. Moore, K. Berwick and H.S. Gamble, "Micro-Raman study of stress distribution generated in silicon during proximity rapid thermal diffusion", *Materials Science and Engineering B*, 2000 (In press).

- 3. T.A. Briantseva, Z.N. Lebedeva, D.V. Lioubtchenko, M. Nolan, T.S. Perova and R.A. Moore, "Precise chemical analysis development for silicon wafers after rapid thermal processing", *Applied Surface Science*, 2000 (In press).

- 4. **M. Nolan**, T.S. Perova, R.A. Moore, C.E. Beitia and H.S. Gamble, "Spectroscopic investigations of borosilicate glass and its application as a dopant source", *J. Electrochem. Soc.*, 2000 (In press).

#### **Referred Conference Proceedings**

M. Nolan, T. Perova, R.A. Moore and H.S. Gamble, "Material and surface analysis

of p-type junctions in silicon formed by rapid thermal diffusion", *Materials Research*Society Proceedings, 30 November–4 December, Boston, C3, 58, (1998).

- 2. **M. Nolan**, T. Perova, R.A. Moore and H.S. Gamble, "Boron diffusion from a spin-on source during rapid thermal processing", *Material Research Society Proceeding of the 2<sup>nd</sup> International Conference on Amorphous and Crystalline Insulating Thin Films*, 12-14 October, Hong Kong, 89, (1998).

- 3. **M. Nolan**, T. Perova, R.A. Moore, C.J. Moore, K. Berwick, H. Byrne and H.S. Gamble, "Micro-Raman study of stress distribution generated in silicon during proximity rapid thermal diffusion", *Proceedings of the European Material Research Society Spring Meeting*, 1-4 June, Strasbourg, France, p. E-21, (1999).

- 4. T. Briantseva, Z. Lebedeva, D. Lioubtchenko, M. Nolan, T. Perova, R.A. Moore and K. Berwick, "Precise chemical analysis development for Si and GaAs surfaces", *Proceedings of the International Congress on Advanced Materials and Processes*, EUROMAT'99, 27-30 September 1999, Munich, Germany (In press).

- T. Briantseva, Z. Lebedeva, D. Lioubtchenko, M. Nolan, T. Perova, R.A. Moore and H.S. Gamble, "Process-induced modification to the surface of crystalline silicon by precise chemical analysis", *Proceedings of the International Congress on Advanced Materials and Processes*, EUROMAT'99, 27-30 September 1999, Munich, Germany (In press).

- M. Nolan, T.S. Perova, C.E. Beitia, R.A. Moore, J. McGilp, H.S. Gamble, C. Moore and K. Berwick, "Spectroscopic investigations of dopant source borosilicate glass", The Electrochemical Society 197<sup>th</sup> Meeting, Toronto, Ontario, Canada, May 14-18, 2000 (Accepted).

- 7. M. Nolan, T.S. Perova, C.E. Beitia, R.A. Moore, J. McGilp, H.S. Gamble, C. Moore and K. Berwick, "Spectroscopic investigations of dopant source borosilicate glass and porous silicon for integrated circuits", NATO Advanced Workshop (ARW)/Spring School "Frontiers of Nano-Optoelectronic Systems: Molecular Scale Engineering and Processes" SA (PST.ARW 975678) 5068, Kyiv, Ykraine, 22-26<sup>th</sup> May, 2000 (Accepted).

- 8. M. Nolan, T.S. Perova, R.A. Moore, H.S. Gamble, D. Lowney, P.J. McNally, T. Tuomi, R. Rantamaki and A.N. Danilewsky, "Micro-Raman and Synchrotron X-Ray Topography of Boron Doped Silicon Wafer using Rapid Thermal Diffusion", The XVIIth International Conference on Raman Spectroscopy, ICORS 2000, Beijing, China, August 20-25, 2000, China (Accepted).

- 9. **M. Nolan**, T.S. Perova, R.A. Moore and H. S. Gamble, "Characterisation of the borosilicate glass as a dopant source and its application for low-doped drain PMOS devices", The 3<sup>rd</sup> International conference on Materials for Electronics, 16-17 October 2000, Dublin, Ireland (Oral presentation)(Submitted).

### Preface

The IC industry continually strives towards manufacturing higher density integrated circuits, since increasing the density of microchips on the wafer increases the profitability of the process. Increasing the density means using shorter channel lengths in MOS transistors. Reducing the channel lengths did not present a major problem until the 1970s, when channel lengths were reduced to  $< 2 \, \mu m$ . Beyond this point the short-channel devices began to display characteristics that were not observed in long-channel devices. These deleterious characteristics were termed short-channel effects, and continue to exacerbate engineers to the present day.

Low-doped drain (LDD) extensions in MOS transistors improve short-channel effects. Initially, it was possible to fabricate these shallow junctions using traditional ion implantation. However, ion implantation is limited for ultra-shallow junctions (< 500 Å), primarily because it generates defects in the lattice that enhance dopant diffusion. In particular, producing ultra-shallow boron junctions is a major challenge confronting researchers, since boron tends to channel through silicon resulting in deep junctions. Alternative doping techniques have been widely reported in the literature.

Rapid thermal processing (RTP) is an important technology for ULSI chip manufacturing, and is increasingly replacing conventional furnace processing. RTP is a single-wafer process, and offers the advantage of better wafer-to-wafer uniformity and better control of ambient and peak temperature. The thermal budget is also minimised during RTP since the wafer is rapidly heated to 1000 °C in 10-20 s, typically. RTP is already widely used for annealing implant damage and for forming high quality silicide layers. Rapid thermal diffusion (RTD) is a prospective technique for ultra-shallow junction formation, primarily because anomalous diffusions are avoided due to the minimal thermal budget, and because it does not introduce unwanted defects into the substrate.

This thesis begins by introducing the difficulties that have arisen in MOS transistor device physics and MOS doping technology, in deep submicron device production. RTD of boron from a borosilicate layer is then investigated as a novel technique for fabricating boron junctions. The main aim of this work is to fabricate high quality ultra-shallow boron junctions. *P-n* junction diodes are fabricated and electrically tested to determine the quality of the junctions. The stress that is generated during RTD is also analysed.

### Chapter 1

### **MOS Transistor Device Physics**

#### 1.1 Introduction

During the past 50 years, the IC industry has aimed towards making smaller and faster devices. In the 1970's MOSFET devices were fabricated with gate lengths smaller than  $\sim$ 2  $\mu$ m. Beyond this point the MOSFETs began to exhibit characteristics that had not been observed in larger long-channel devices. These characteristics were termed short-channel effects. Short-channel effects deteriorate as the gate length continues to decrease. To date, MOS devices with gate lengths less than 0.25  $\mu$ m have been manufactured, and short-channel effects have become a critically important issue. Therefore, an understanding of MOS device physics becomes increasingly important in sub-quarter-micron VLSI and ULSI technology. Device aspects that could once be ignored, such as source-drain doping profiles, are now extremely significant.

Shallow junctions eliminate short-channel effects in MOS devices. The main aim of this work is to fabricate shallow boron junctions for PMOS transistors. Therefore, this chapter tends to put more emphasis on PMOS devices

This chapter begins by discussing MOS capacitors, since an understanding of a MOS capacitor is central to understanding the operation of a MOSFET. Secondly, long-channel MOSFETs are discussed. Thirdly, short-channel MOSFETs and issues of MOSFET device scaling are presented. Finally, lightly-doped-drain (LDD) devices are presented. LDD devices are the most widely used devices for improving the reliability and device performance of short-channel MOSFETs.

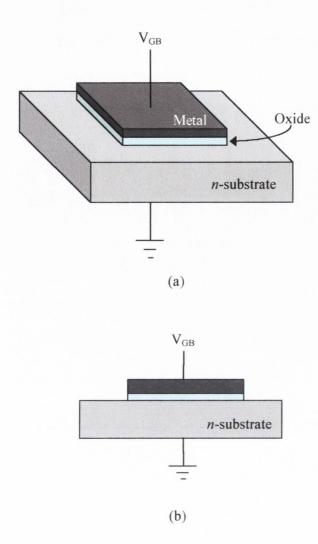

Figure 1.1. (a) Perspective view of a MOS-C, (b) Cross-section of a MOS-C.

### 1.2 MOS Capacitor

The MOS capacitor (MOS-C) exhibits behaviour that is the foundation of both long-and short-channel MOSFET operation. Such behaviour is easiest to describe in a MOS-C since some of the more complex MOS device characteristics are absent in the MOS-C. Figure 1.1 shows the structure of a MOS-C. It consists of a metal conducting layer (referred to as the gate), an insulating layer (usually silicon dioxide) and a semiconductor substrate, hence the acronym MOS (*metal-oxide-semiconductor*). The semiconductor substrate may be *n*-type or *p*-type. Originally, the gate in the early MOS-C structure was made of aluminium metal, however, polysilicon has replaced aluminium in modern MOS structures, but the original MOS acronym remains unchanged. Figure 1.1 shows

terminals connected to the gate and to the substrate of the MOS-C. An external bias,  $V_{GB}$  (gate-body voltage), can be applied across these terminals. Sections 1.2.1-1.2.4 will consider the operation of a n-substrate MOS-C, Fig. 1.1.

#### 1.2.1 Accumulation

In the first biasing case a positive bias is applied ( $V_{GB}>0$ ). The positive bias causes electrons (the majority carriers in *n*-type Si) to be attracted to the Si surface adjacent to the oxide. More electrons accumulate near the Si surface than if  $V_{GB}=0$ . The effect of attracting additional majority carriers to the semiconductor surface is called *accumulation*. The conductivity of the region near the Si surface is increased by the presence of the extra electrons.

#### 1.2.2 Depletion

In the second bias condition, a small negative voltage is applied to the gate of the n-type MOS-C ( $V_{GB}$ <0). This causes electrons in the semiconductor to be repelled from the surface, creating a depletion region, of width d, consisting of positively charged donor ions. This mode of operation of called the *depletion* mode.

#### 1.2.3 Inversion

When the negative voltage that is applied to the gate is increased, minority holes are attracted to the Si surface and the Si surface is changed from n-type to p-type. This layer of holes at the Si surface is called the *inversion layer*.

#### 1.2.4 Strong Inversion

If  $V_{GB}$  is made even more negative, the hole density per unit volume at the surface will be equal to the electron density in the bulk. This is known as the point of *onset of strong inversion*. When strong inversion occurs, the depletion region reaches a maximum width of  $d_{max}$ . The voltage applied between the gate and the substrate at the onset of strong inversion is called the threshold voltage,  $V_T$ . For further increases in negative voltage, the hole concentration in the inversion layer exceeds the bulk equilibrium electron concentration, but there is no further change in the depletion width. This mode of operation is referred to as *strong inversion*.

Figure 1.2. (a) Perspective view of a MOSFET, (b) Cross-section of a MOSFET.

### 1.3 Long-Channel MOSFET

Figure 1.2 shows the cross-section of a *p*-channel MOSFET. The important difference between the MOS-C and the MOSFET is that in the latter a *pn* junction exists at each side of the MOS-C channel region. The MOSFET has four terminals, referred to as the source S, gate G, drain D, and the substrate/body B. The source contact will be used as a reference throughout this section. When no voltage is applied to the gate, the source-to-drain electrodes correspond to two back-to-back pn junctions. The only current that can

(b)

flow from source to drain is the reverse leakage current. When a sufficiently large negative voltage is applied to the gate  $(V_{GB}>V_T)$ , the central MOS structure is inverted forming a surface inversion channel that connects the source and drain regions together. A drain current,  $I_D$ , can then flow if a voltage,  $V_{DS}$ , is applied between the source and drain terminals.

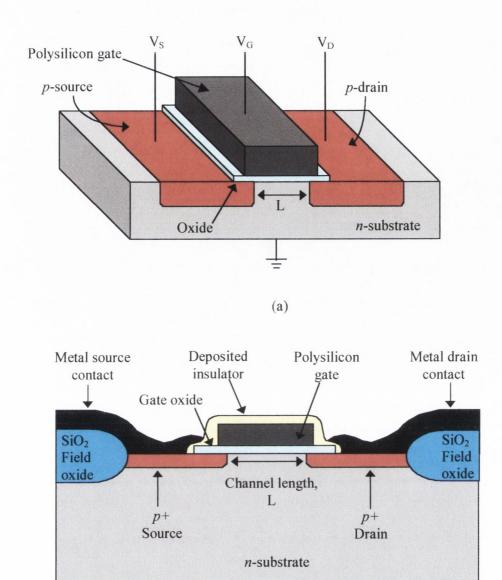

Now, the  $I_D$  variation with  $V_{DS}$  will be considered. When  $V_{DS} = 0$  V,  $I_D = 0$ , even if  $V_{GS} > V_T$ . When  $V_{DS}$  is increased slightly  $I_D$  starts to flow. When  $V_{DS}$  is small (i.e. a few tenths of a volt or less), the surface channel behaves like a simple resistor. Therefore, an  $I_D$  proportional to  $V_{DS}$  flows into the drain. A plot of  $I_D$  against  $V_{DS}$ , Figure 1.3a, is used to demonstrate the  $I_D$ - $V_{DS}$  behaviour; the response to small values of  $V_{DS}$  is shown as the straight line from the point 0 to the point A.

When  $V_{DS}$  is increased above a few tenths of a volt, the MOSFET exhibits a new phase of behaviour. Current flowing in the channel gives rise to a significant voltage drop in the channel. Specifically, the channel voltage is  $V_{SB}$  at the source end and  $V_{DB}$  at the drain end. Since,  $V_{SB} = 0$  V and  $V_{DB} < 0$  V, the channel voltage equals 0 V at the source end, and increases to  $V_{DB} < 0$  V at the channel end. As shown in Figure 1.3c, the voltage increase across the channel causes the depletion region under the gate to widen towards the drain end of the channel. As the depletion width increases, more positively charged donor ions are uncovered. Since  $V_{GB}$  is fixed, the total charge in the semiconductor must remain unchanged to maintain balance with the unchanged value of the charge on the gate. Therefore, the mobile carrier concentration in the inversion layer decreases as the width of the depletion region increases. The smaller number of mobile carriers causes the channel conductance to decrease, which in turn is manifested as a smaller slope in the  $I_D$ - $V_{DS}$  characteristic as  $V_{DS}$  is increased. As the drain voltage is increased further, the depletion region continues to widen and the slope of the I-V characteristic continues to decrease.

Eventually, if  $V_{DS}$  is increased sufficiently, the width of the inversion layer is reduced to zero in the vicinity of the drain, Fig 1.3d. The reduction of the inversion layer width to zero due to an increase in  $V_{DS}$  is called pinch-off. The pinch-off point on the  $I_D$ - $V_{DS}$  characteristic is shown at point B in Figure 1.3a. As the drain voltage increases beyond

**Figure 1.3.** (a)  $I_D$ - $V_{DS}$  characteristic of a MOSFET being operated at a fixed  $V_{GS}$ > $V_T$ ; (b)  $V_{DS}$ =0 V; (c) inversion layer narrowing under moderate  $V_{DS}$  biasing; (d) pinch-off,  $V_{DS}$ = $V_{DSSAT}$ ; and (e) post pinch-off,  $V_{DS}$ > $V_{DSSAT}$ .

the pinch-off voltage  $V_{DSSAT}$ , the pinch-off section of the channel widens from a point into a segment,  $\Delta L$  in length, Figure 1.3e. Most of the voltage drop in excess of  $V_{DSSAT}$  is dropped across this pinched-off section  $\Delta L$ .  $I_D$  remains approximately constant (saturated) for drain voltages greater than  $V_{DSSAT}$  so long as  $\Delta L \ll L$ . If  $\Delta L$  becomes comparable to L (which may occur in short-channel MOSFETs), the same voltage drop appears across a shorter channel, and the post-pinch-off current  $I_{DSAT}$  in such devices will increase as  $V_{DS}$  is increased above  $V_{DSSAT}$ , Figure 1.3a.

For each value of  $V_{GS} > V_T$ , a characteristic of the form shown in Figure 1.3a will be observed. Since the conductance of the channel will increase as  $V_{GS}$  is increased, the initial slope of  $I_D$  will also become steeper with increasing  $V_{GS}$ . Also, since the inversion layer contains more holes, a larger value of  $V_{DS}$  is needed to produce a pinch-off, and  $V_{DSSAT}$  increases for increasing  $V_{GS}$ . Based on these phenomena, Figure 1.4 shows I-V characteristics of an ideal long-channel MOSFET.

#### 1.3.1 Subthreshold Currents in Long-Channel MOSFETs

In section 1.2.4, the onset of strong inversion was defined as the point when the hole density per unit volume at the surface is equal to the electron density in the bulk. The voltage applied between the gate and the substrate at the onset of strong inversion was defined as  $V_T$ . The mode of operation when the hole density at the surface is smaller than the electron density in the substrate is referred to as weak inversion. Since mobile carriers can exist in the channel region below threshold (i.e., in weak inversion), a small

**Figure 1.4.** I<sub>D</sub>-V<sub>DS</sub> characteristics for a long-channel MOSFET.

drain current can flow in the channel if a voltage is applied to the drain. This small current is called the subthreshold current,  $I_{DST}$ . In most applications  $I_{DST}$  is far too small to be useful as a drive current. However, it can represent an unwanted leakage current. The common range of  $V_T$  in submicron CMOS ICs is 0.6-0.8 V. Therefore, when  $V_{GS} = 0$  V the MOSFETs in the circuits may be close to weak inversion. Consequently, it is critical to be able to establish and maintain a uniform and stable  $V_T$  in MOSFET devices. If the magnitude of  $V_T$  drops even slightly below its designated value, the device may exhibit excessive subthreshold leakage current when  $V_{GS} = 0$  V. Factors that may adjust the threshold voltage are discussed in Section 1.4.

#### 1.4 Short-Channel MOSFET

The continuous drive by the IC industry towards higher device densities and faster circuits increases the importance of MOSFET device scaling. As mentioned in the Introduction, in the 1970s MOS transistors with gate lengths less than 2 µm began to exhibit characteristics that were not observed in larger long-channel devices. The control of these short-channel effects is critical in todays sub-quarter-micron technology. This section will discuss these short-channel effects and the resulting device degradation.

#### 1.4.1 Hot-Carrier Effects

If MOSFET device dimensions are reduced and the voltage supply remains constant, the lateral drain applied electric field in the channel increases. A large drain applied electric field exists in submicron short-channel MOSFETs. Mobile carriers injected from the source gain kinetic energy from this and are accelerated towards the drain. Some of the carriers can gain sufficient energy to surmount the Si-SiO<sub>2</sub> barrier and are injected into the gate oxide, where they may be trapped. Those carriers trapped in the gate oxide are detrimental for the device since they may lead to a  $V_T$  shift and deterioration in transconductance,  $g_m$  ( $g_m = \delta I_{DS}/\delta V_{GS}$ ). As mentioned in Section 1.3.1, if the magnitude of  $V_T$  drops even slightly below its designated value, the device may exhibit excessive subthreshold leakage current when  $V_{GS} = 0$  V. Other injected carriers flow towards the gate electrode contributing to the gate current. Those carriers flowing to the gate electrode may generate trapping sites in the oxide and at the interface. Figure 1.5 shows

Figure 1.5. Cross-section of a PMOS transistor showing hot-carrier processes.

these effects schematically. Hole injection into the oxide is far less probable than electron injection because the potential energy barrier for holes at the Si-SiO<sub>2</sub> interface is higher.

Those carriers not injected into the gate oxide can continue accelerating towards the drain, causing avalanche multiplication as a result of impact ionisation, Fig. 1.5. Thus, a large number of electron-hole pairs are generated. Some of the electrons and holes are injected into the gate oxide and become trapped there. Some flow to the gate electrode appearing as a gate current. The majority of the generated carriers flow to the drain, contributing to drain current. Those carriers flowing to the substrate become a substrate current. Excessive substrate current may induce latchup in CMOS circuits. Secondly, as some of the carriers are accelerated leaving the drain-substrate depletion region, they may gain enough energy to cause secondary impact ionisation far from the drain region. Some of the electrons generated in this manner may then travel to other nodes on the chip to be collected. This may lead to the reduction of storage time of dynamic circuit nodes in DRAMs.

Hot-carrier effects are observed in NMOS transistors with gate lengths  $< 2 \mu m$ , however, they are only observed in PMOS transistors with gate lengths  $< 1 \mu m$ . The reasons for this are that impact ionisation due to holes is 1-2 orders of magnitude lower than that due to electrons at a given electric field.

There is one particular hot-carrier effect that only occurs in PMOS transistors [1]. Hot electrons that are trapped in the gate oxide cause a build-up of negative charge in the oxide near the drain. This charge eventually inverts the n-type Si surface near the drain, resulting in an extension of the  $p^+$  drain region, Fig. 1.6. As a result, the effective channel length, L, shrinks. A reduction in L at low gate voltages is undesirable for short-channel PMOS devices since it gives rise to a poor subthreshold characteristic and a reduction in the source-drain punchthrough voltage (Section 1.4.3). A second effect arising from the build-up of negative charge in the oxide of the PMOS is that the magnitude of  $V_T$  is reduced.

In summary, hot-carrier effects cause serious device degradation. Oxide trapped charges cause detrimental shifts in the threshold voltage and deterioration in transconductance. Carriers that flow towards the gate electrode may generate oxide and interface trapping sites as they move through the gate oxide. Carriers that contribute to the substrate current may induce latchup in CMOS circuits. These carriers may also generate electronhole pairs by secondary impact ionisation far from the drain. The generated electrons may then escape the drain field and cause device deterioration in other parts of the chip.

**Figure 1.6.** Hot electron injection into the gate oxide in a PMOS transistor.

Lightly doped drain (LDD) structures have been used to increase the hot-carrier reliability in submicron MOSFETs. LDD devices will be presented in Section 1.5.

## 1.4.2 Drain-induced-barrier-lowering (DIBL)

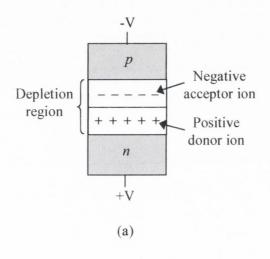

In an ideal MOSFET device the electric field lines emanating from the charge under the gate would terminate on the gate charge. However, in real devices some terminate on space charge in the source and drain depletion regions. Figure 1.7 shows this effect schematically. A *pn* junction depletion region consists of positively charged donor ions

Figure 1.7. (a) Reverse biased pn junction; (b) Cross section of a PMOS transistor showing electric field lines from the channel charge terminating on acceptor ions in the source and drain depletion regions.

and negatively charged acceptor ions. In a PMOS transistor the electric field lines emanating from the positive donor ions in the channel depletion region can terminate on the negatively charged acceptor ions on the p-type side of the source and drain depletion regions instead of on the gate charge, Fig. 1.7. Consequently, less gate charge is required to cause inversion, thus reducing the magnitude of  $V_T$ . This effect is called drain-induced-barrier-lowering (DIBL). The fraction of the charge induced by the source and drain becomes significant as the channel length is of the order of the junction depletion widths. Therefore, DIBL critically degrades submicron MOS devices.

LDD devices suppress DIBL in submicron MOSFETs, and will be discussed in Section 1.5.

# 1.4.3 Punchthrough

In Section 1.3.1, subthreshold currents,  $I_{DST}$ , in long-channel MOSFETs were described. In weak inversion ( $V_{GS} < V_T$ ) a subthreshold current may flow at the surface of the channel region. If  $V_{GS}$  is fixed and  $V_{DS}$  is increased, larger values of  $I_{DST}$  are observed in short-channel MOSFETs than in long-channel devices. This larger  $I_{DST}$  is partly due to an increase in DIBL. However, another short-channel effect called punchthrough can also give rise to the increase in  $I_{DST}$ .

When  $V_{DS}$  in increased in MOSFETs with  $L<2~\mu m$  the source and drain depletion region edges get closer together and eventually merge. Since the depletion regions of a pn junction widen as the reverse bias is increased, all MOSFETs would eventually enter punchthrough if a sufficiently high  $V_{DS}$  was applied. However, in MOSFETs with  $L>2~\mu m$ , junction breakdown usually occurs before the punchthrough voltage is reached. Consequently, punchthrough is not a limiting factor in long-channel devices. In shorter channel devices,  $L<2~\mu m$ , punchthrough does represent a serious limitation.

The next section will discuss changes that have been made to submicron MOS devices in an attempt to suppress punchthrough and the other short-channel effects that have been presented in the previous sections.

Figure 1.8. Cross-section of a LDD PMOS transistor.

# 1.5 Lightly Doped Drain (LDD) Devices

The problems that have arisen in submicron MOSFETs have put enormous pressure on process and design engineers to make modifications to the basic MOSFET structure that will improve the reliability and performance of these smaller devices. Use of a lightly doped drain (LDD) is one of the modifications that have been investigated. The remainder of this section will describe the LDD MOSFET structure and explain its impact on device performance. LDD device fabrication will be discussed later in Chapter 8.

Figure 1.8 shows a cross section of a conventional LDD PMOS transistor. A shallow lightly doped region has been added to the source and drain. LDD structures are the most widely used device structures for increasing hot-carrier reliability in submicron MOSFETs. Figure 1.9 shows the electric field profile at the drain of a MOSFET, both with and without a LDD structure [2]. In this case, the LDD provides a 30-40% reduction in the drain-applied electric field. A large proportion of the drain-source voltage drop is across the LDD. As a result, a mobile carrier that is injected from the source into the channel will not gain sufficient energy from the lower drain applied electric field to become a hot-carrier. Therefore, the hot-carrier reliability of the device is increased. Figure 1.10 shows the hot-carrier lifetime improvement gained by using a *p*-channel LDD [1]. It compares conventional 0.95 μm PMOS devices with 0.8 μm LDD

**Figure 1.9.** Magnitude of the electric field at the Si-SiO<sub>2</sub> interface as a function of distance:  $L = 1.2 \mu m$ ,  $V_{DS} = 8.5 V$ ,  $V_{GS} = V_T$  [2].

**Figure 1.10.** Device lifetime versus reciprocal stressing drain voltage for a conventional PMOSFET and a LDD PMOSFET [1].

PMOSFETs. The LDD devices have superior reliability despite the shorter gate lengths, and an extrapolation of the data to  $V_{DS} = 5$  V implies that lifetimes in excess of 10 years are possible. Unfortunately, while LDDs do improve the hot-carrier reliability in submicron devices, they also cause an unwanted reduction in the drain current. LDD regions increase the total resistance along the channel, thus, reducing  $I_D$ . Several improvements have been made to the conventional LDD device shown in Figure 1.8, including increasing the LDD doping concentration. These improvements will be discussed in Chapter 8.

DIBL critically degrades submicron devices by lowering the threshold voltage, Section 1.4.2. DIBL can be reduced by fabricating shallow drain junctions in the MOS transistor. However, reducing the drain junction depth also degrades the device performance. The reduced junction depth increases the sheet resistance and the contact resistance of the drain. The shallower junction is also more susceptible to aluminium junction spiking. Another way to achieve a shallow junction in a PMOS device is to use a LDD. The junction depth of the shallow LDD reduces unwanted DIBL and also avoids the issues that arise when the entire  $p^+$  drain junction depth is decreased.

Figure 1.11. Punchthrough voltage as a function of boron implant dose for a 0.4  $\mu m$  PMOSFET with and without an LDD structure [3].

Table 1.1 Projected LDD junction depths versus gate lengths [4].

| Year of first<br>product<br>shipment | 1997               | 1999               | 2001               | 2003               | 2006               | 2009               | 2012               |

|--------------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| Gate Length (µm)                     | 0.25               | 0.18               | 0.15               | 0.13               | 0.1                | 0.07               | 0.05               |

| LDD junction<br>depth (Å)            | 500-1000           | 360-720            | 300-600            | 260-520            | 200-400            | 150-300            | 100-200            |

| LDD Conc. (cm- <sup>3</sup> )        | 1x10 <sup>18</sup> | 1x10 <sup>19</sup> | 1x10 <sup>19</sup> | 1x10 <sup>19</sup> | 1x10 <sup>20</sup> | 1x10 <sup>20</sup> | 1x10 <sup>20</sup> |

Solutions exist Solutions being persued No known solution

Reducing the source/drain junction depths also suppresses punchthrough in MOS transistors. Shallow junctions reduce the lateral spread of dopants under the gate. Therefore, the lateral spread of the source/drain depletion regions is reduced, making MOSFETs less susceptible to punchthrough. However, the entire length of the source/drain junctions is not made shallow, to avoid junction series resistance and junction leakage problems as mentioned above. So, once again, a LDD structure is a more suitable way to achieve shallow junctions. Figure 1.11 indicates that the punchthrough voltage is increased by 2-3 V when an LDD is incorporated into a PMOS device [3].

In summary, LDDs improve the reliability and device performance of submicron MOSFET devices. Table 1.1 shows the projected junction depths for LDDs for the next few generations of technology [4].

# 1.6 Conclusions

In submicron MOS technology, devices exhibit characteristics that were not observed in larger long-channel devices. These characteristics are termed short-channel effects. Hot-carrier effects, drain-induced-barrier-lowering (DIBL), and punchthrough are some of the

short-channel effects that have been observed in MOS transistors. These effects degrade device performance and reduce reliability.

Hot-carrier effects cause a detrimental shift in threshold voltage. If the magnitude of  $V_T$  drops even slightly below its designated value, the device may exhibit excessive subthreshold leakage current when  $V_{GS} = 0 \text{ V}$ . Hot-carrier effects also deteriorate transconductance and change the substrate, drain and gate currents. Excessive hot-carrier generated substrate current may induce latchup in CMOS circuits.

The second short-channel effect that was discussed was DIBL. DIBL also causes an unwanted harmful shift in threshold voltage. Finally, as the gate length is reduced, MOS devices become more susceptible to punchthrough. Punchthrough increases the subthreshold leakage current in short-channel MOSFETs.

Lightly doped drain (LDD) devices have been used to improve device performance and reliability in submicron MOS transistors. They eliminate hot-carrier effects by reducing the drain-applied electric field across the MOS channel. The shallow LDD junction depth reduces DIBL. LDDs also reduce the lateral spread of the source/drain depletion regions, making MOSFETs less susceptible to punchthrough. The disadvantage of introducing LDD into the conventional MOSFET structure is that the LDD causes an unwanted reduction in the drain current. Improvements that have been made to the conventional LDD MOSFET will be discussed later in Chapter 8. Fabrication of *p*-type LDDs is extremely challenging due to the high diffusivity of boron in silicon. This doping technology issue will be presented in the following chapter.

## References

- [1] M. Koyanagi, A.G. Lewis, R.A. Martin, T.-Y. Huang and J.Y Chen, *IEEE Trans. Electron. Dev.*, **ED-34**, 839, (1987).

- [2] S. Ogura, P.J. Tsang, W.W. Walker, D.L. Critchlow and J.F. Shepard, *IEEE Trans. Electron. Dev.*, **27**, 1359, (1980).

- [3] A. Schmitz and J.Y. Chen, *IEEE Trans. Electron. Dev.*, **ED-33**, 148, (1986).

[4] The National Technology Roadmap for Semiconductors, Semiconductor Industry Association, (1997), p. 74.

# Chapter 2

# MOSFET Doping Technology

# 2.1 Introduction

Ion implantation has been the method of choice for doping semiconductor devices for more than 20 years, due to its unquestionable advantage of precise concentration control and reproducibility. However, for ultra-shallow junctions it has limitations related to defect formation in the target crystal, which affect both junction depth and electrical properties of devices. In particular, shallow *p*-type junction formation through boron implantation creates difficulties. In an attempt to avoid these problems, alternative doping techniques that produce shallow defect-free junctions have been investigated. This chapter discusses the difficulties that have arisen when using ion implantation to fabricate shallow junctions. Rapid thermal doping techniques are also discussed as an alternative to ion implantation.

# 2.2 Ion Implantation

Ion implantation is a process by which energetic impurity atoms can be introduced into a semiconductor substrate. As an energetic ion penetrates a solid target material, it transfers energy by Coulombic interaction with the electrons in the target material (*Electronic Stopping*) and by collisions with the target nuclei (*Nuclear Stopping*), and eventually come to rest. In electronic stopping, the energy transferred to the electrons can lead to excitation of the electrons to higher energy levels, or to ionisation of the electrons. The energy loss due to these electronic interactions gradually slows the ion, eventually bringing it to a stop. In nuclear stopping, the transfer of energy to the atomic nuclei causes a deflection of the projectile ion and also dislodges the target nuclei from

their original sites. Consequently, nuclear stopping results in physical damage to the semiconductor, which may take the form of point or line defects. Often the semiconductor can become amorphous and/or semi-insulating as a result of this process.